#### FROM MEMORY TECHNOLOGY AND ARCHITECTURE TO COMPUTING WITH NON-VOLATILE MEMORY

Pr. Lionel TORRES, lionel.torres@umontpellier.fr

Thanks to : S. Senni, G. Patrigeon, F. Ouattara, G. Sassatelli, A. Gamatié, J.Y Peneau, M. Robert, P. Benoit

ARCHI 2017 - Nancy

# Summary

- 1 Context and objectives of the lecture

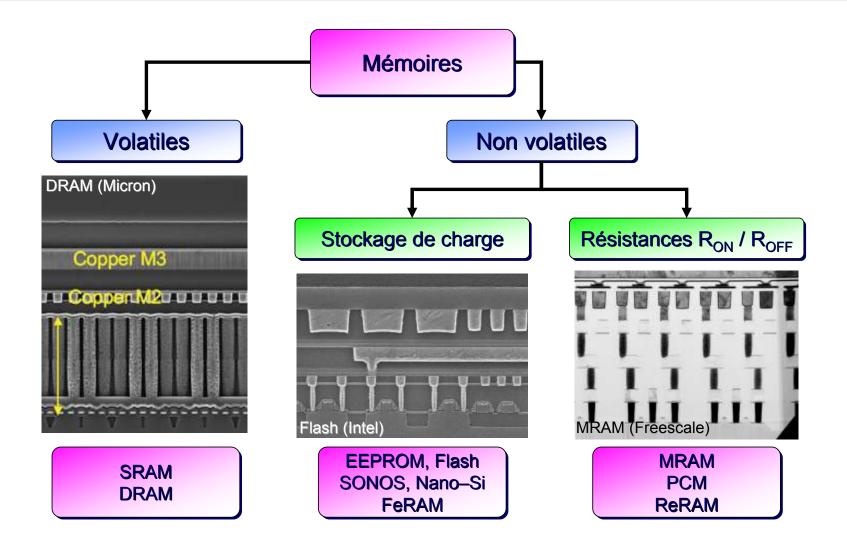

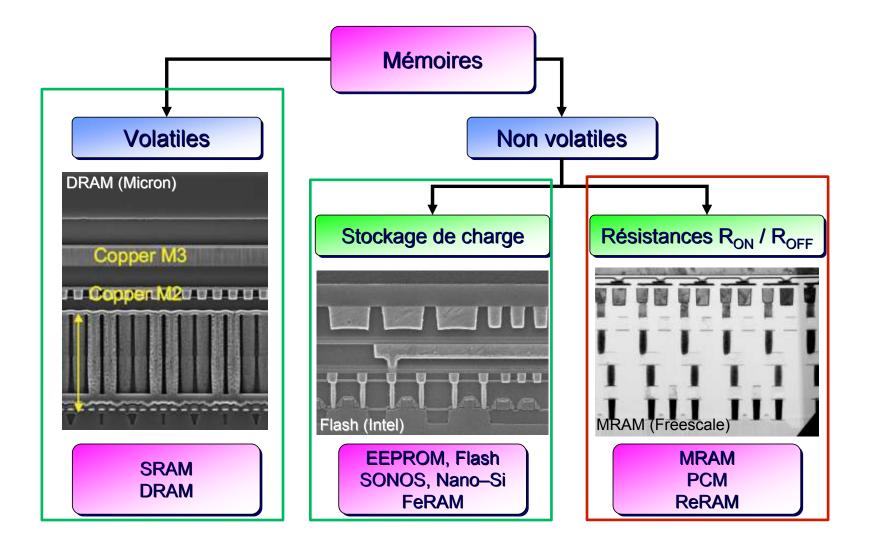

- 2 Classical technologies and memory architecture overview (SRAM, DRAM, FLASH)

- 3 Emerging memory technologies

- 4 Computing with Non-Volatile memory technologies

- For high performance computing applications

- For Embedded applications (Non-volatile processor)

- For secure applications

- 5 Conclusions

## 1- Context

# 1- Context

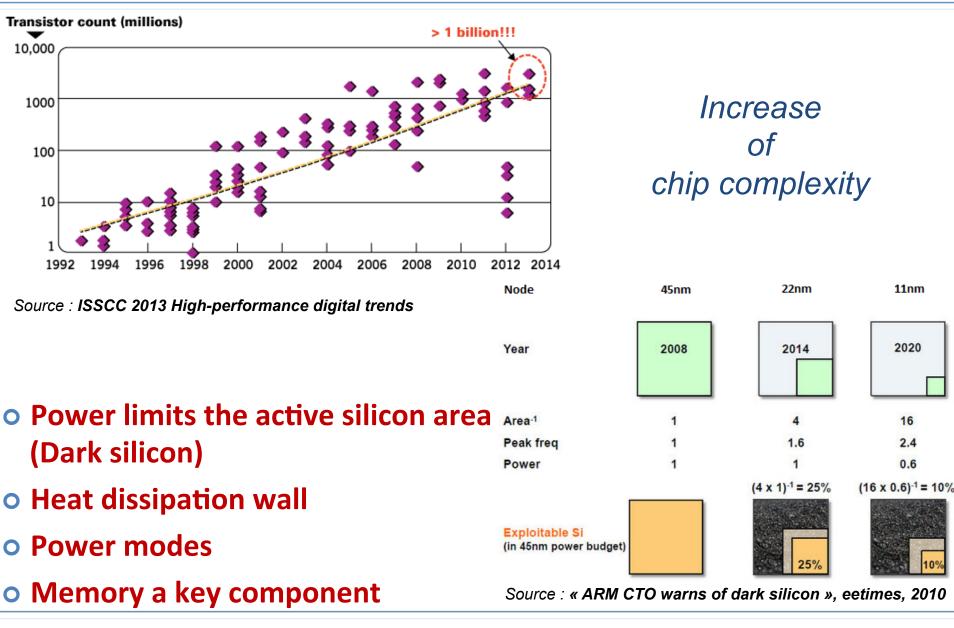

#### Observation

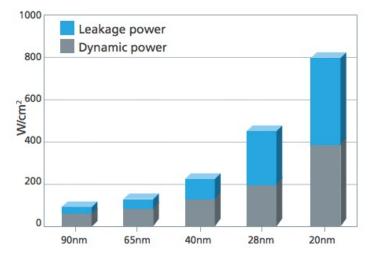

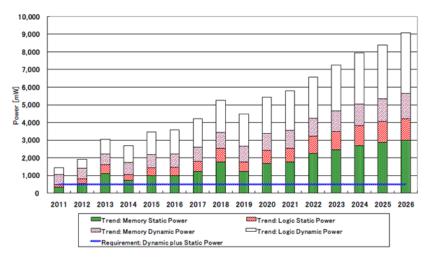

- Decreasing size of devices

- → power consumption and heat issues

- → stagnation of performance

- Why?

- Leakage current of CMOS devices

- Volatility

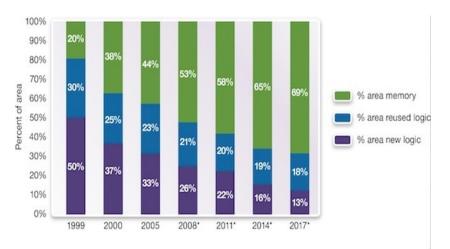

#### Memory: a key component

Source : Semico Research Corporation

Figure 1: Leakage power becomes a growing problem as demands for more performance and functionality drive chipmakers to nanometer-scale process nodes (Source: IBS).

Source : ITRS

## 1- Context

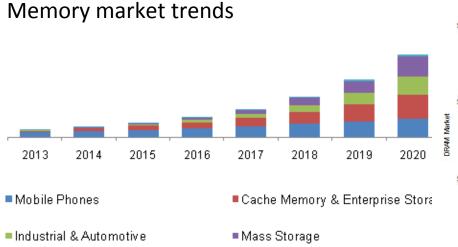

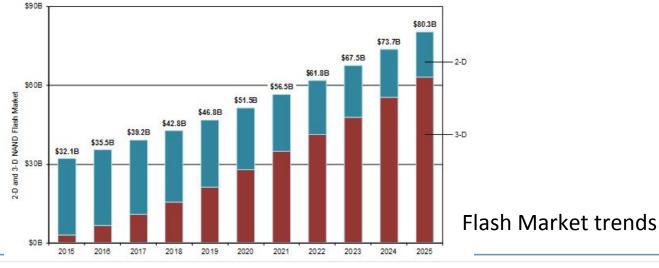

#### DRM market trends

#### 7-mars-17

Embedded MCU & Smart Card

1/ Giving a memory technology architecture overview

2/ Discussing on promising memory technologies

3/ Understanding which type of memory technologies related to applications

4/ Illustrating some case study to demonstrate that logic in memory could help to reach ultra low power consumption applications

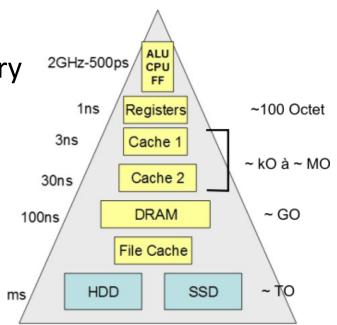

#### **Memory Hierarchy**

- Closer the memory is to computing/calcul, the faster it must be

- Processor Registers are part of the memory hierarchy

- SRAM Cache memory connected to the processor

- Main memory in general is DRAM

- Data storage, slow but very dense, Nonvolatile memory

- What is important : the cell regularity !

T.Kawahara, IEEE Design and test of computers, 52, Janv/Feb 2011)

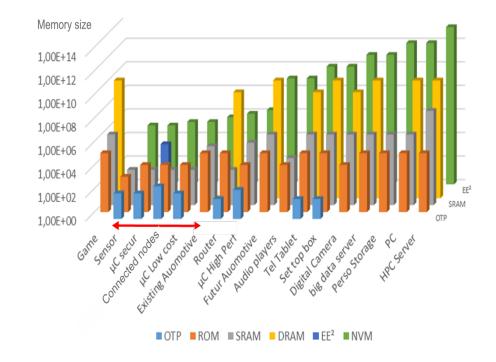

## Memory & applications requirements

### • Main metrics

- Cost

- Performances

- Data retention

- Security

- Physical behaviour

- Power consumption

- Celle size

- Scalability

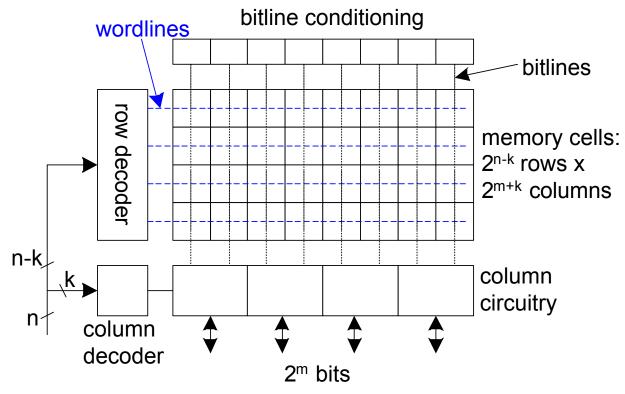

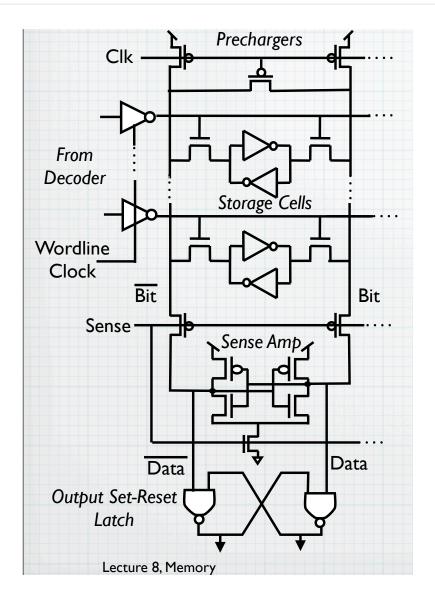

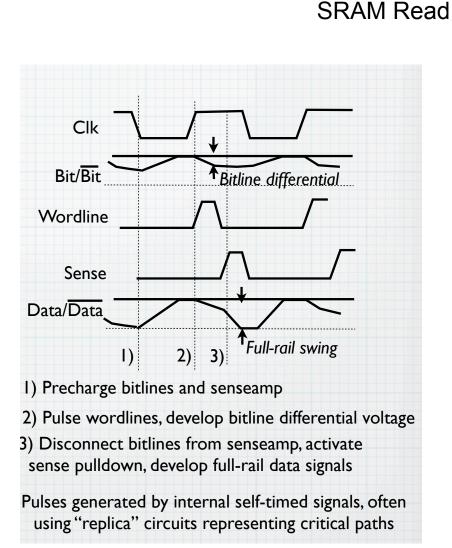

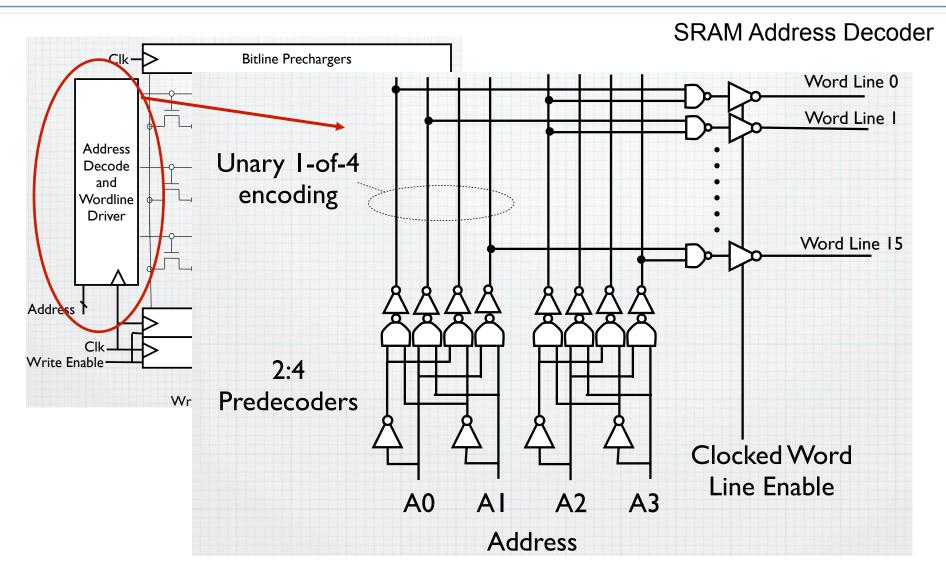

Memory array architecture

- 2<sup>n</sup> words of 2<sup>m</sup> bits each

- If n >> m fold by 2<sup>k</sup> into fewer rows of more columns

- What is important : the cell regularity !

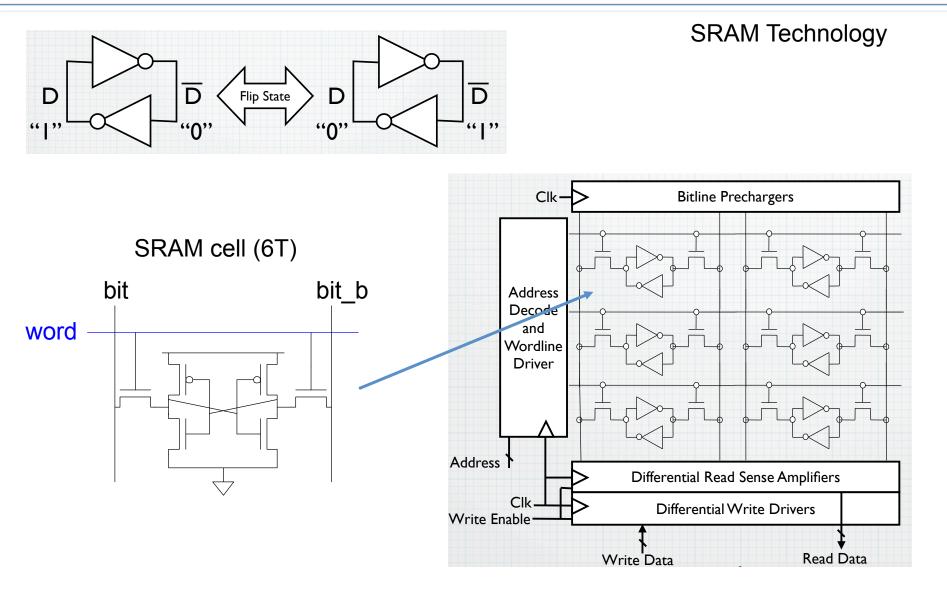

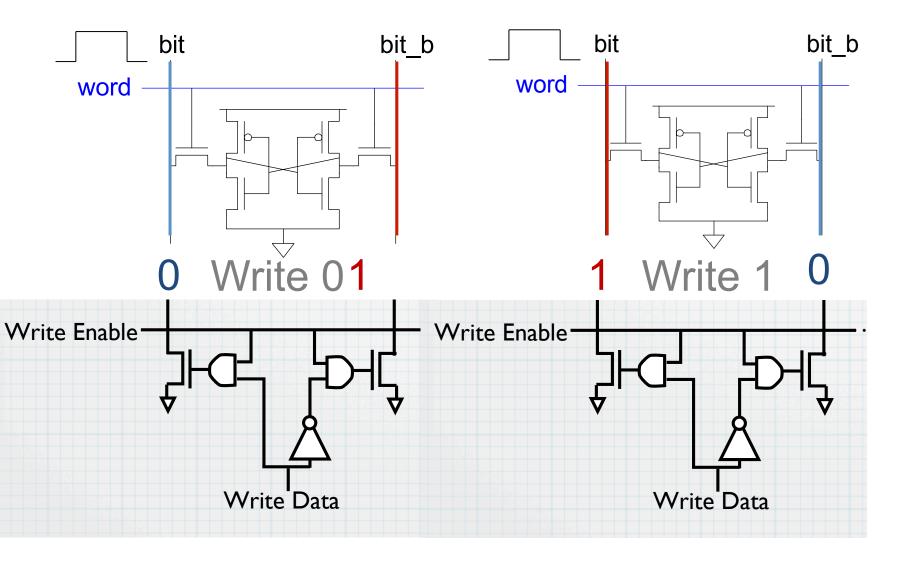

SRAM Write

|   | Bit cells | D<br>e<br>c | Bit cells | Bit cells | D<br>e<br>c | Bit cells |  |

|---|-----------|-------------|-----------|-----------|-------------|-----------|--|

|   | I/O       |             | I/O       | I/O       |             | I/O       |  |

|   | Bit cells | D<br>e<br>c | Bit cells | Bit cells | D<br>e<br>c | Bit cells |  |

|   | Bit cells | D<br>e<br>c | Bit cells | Bit cells | D<br>e<br>c | Bit cells |  |

| C | I/O       |             | I/O       | I/O       |             | I/O       |  |

|   | Bit cells | D<br>e<br>c | Bit cells | Bit cells | D<br>e<br>c | Bit cells |  |

- Using Banks and sub-banks to construct larger array

- Due to RC delays 128-256 bits in row/column (sub-banks)

- For energy efficiency only one Bank (sub-bank) activated at same time

- Delay and energy dominated by I/ O wiring

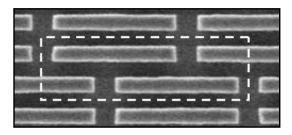

#### SRAM Layout memory

0.092 um<sup>2</sup> SRAM cell for high density applications

0.108 um<sup>2</sup> SRAM cell for low voltage applications

#### Intel 22 nm SRAM

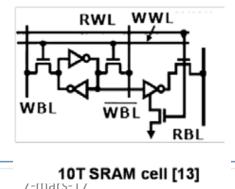

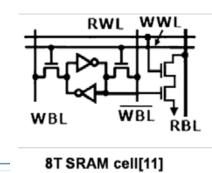

#### **SRAM** limitations

- Static Noise margins

- Very high sensibility to process variability

- High sensibility to temperature

- High Leakage for advance node technology

- To overcome these drawbacks number of Tr per cell increase !

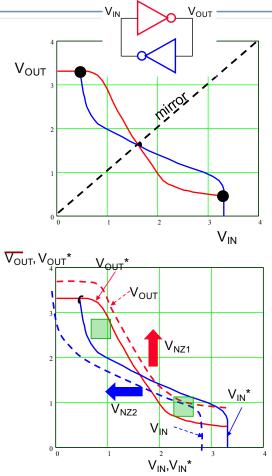

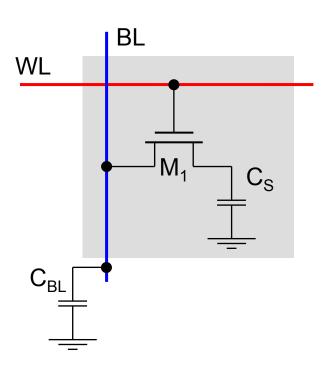

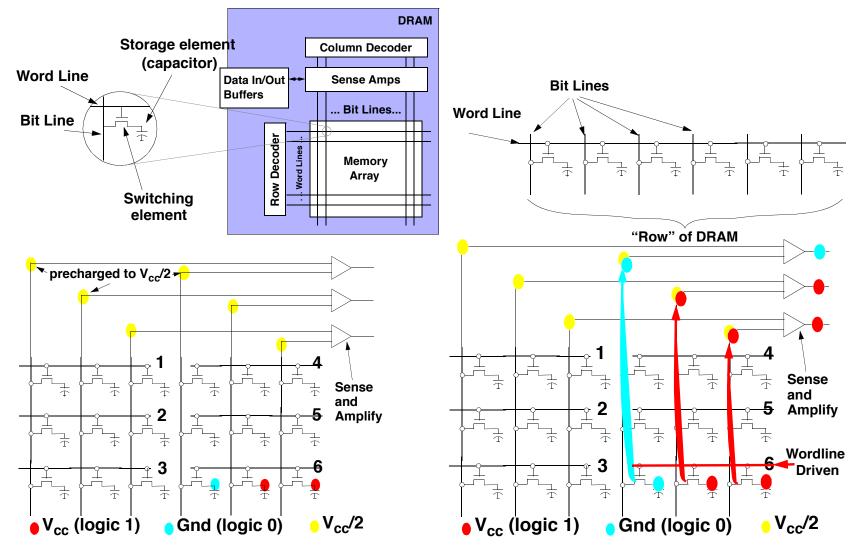

#### **DRAM** Technology

- To write  $-W_L = V_{DD}$ ,  $B_L$  is "0" or "1" depending of the value to store

- To read  $VB_L$  precharged at  $V_{PRE}$ Then activate  $W_L$

- If "1"  $V_{BL}$  1 is detected

- If "0"  $V_{BL}$  0 is detected

1 – Necessary to refresh the cell (~ms)

2 – When a read occurs (destructive read), it is necessary to re-write the cell

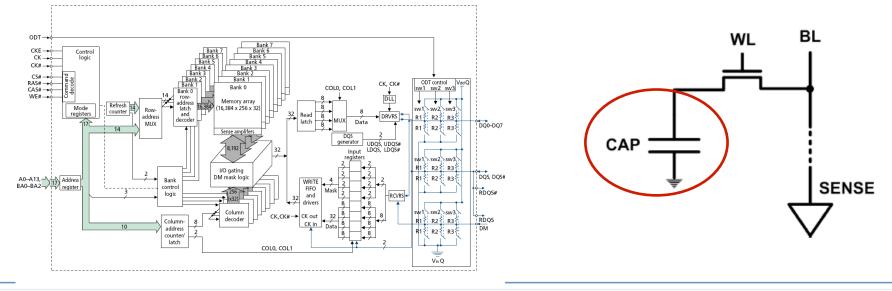

#### **DRAM** Technology

**DRAM** limitations

- Capacitor integration (must be large enough)

- Refresh cost is depending of the capacitor

- Access transistor large to avoid static leakage

- DRAM Hard to scale in advance node

- Not easy to embed DRAM (Specific Techno)

20

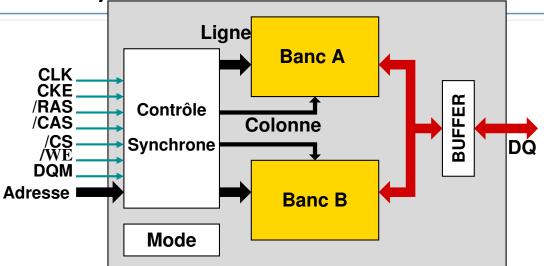

#### SDRAM

- interleaved (2 banks)

one is refreshing and the other can be accessed

- synchronized to clock and burst mode (without CAS)

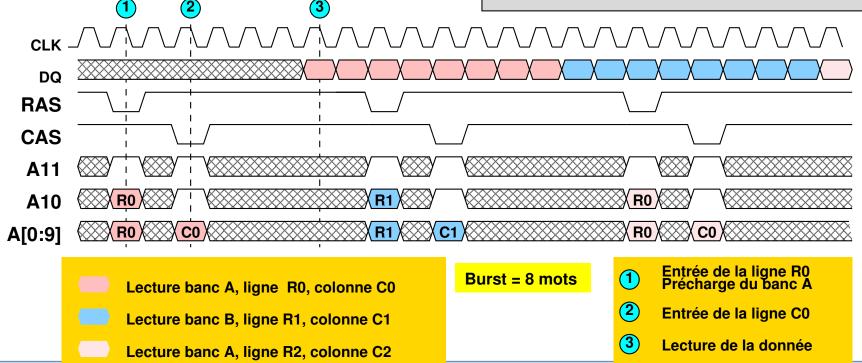

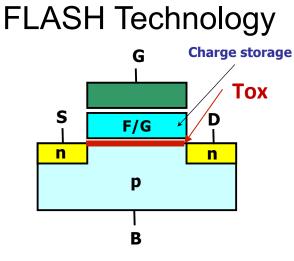

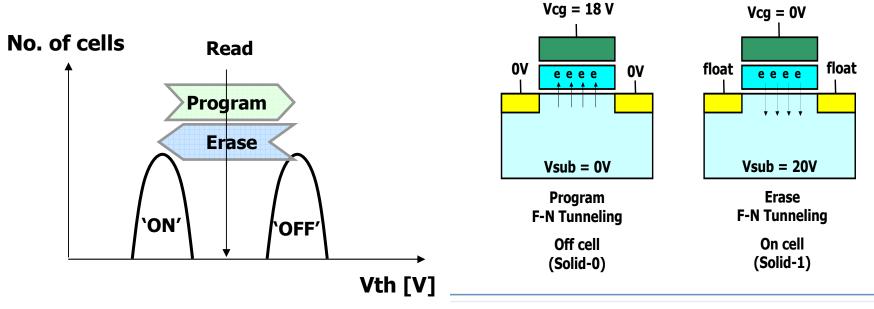

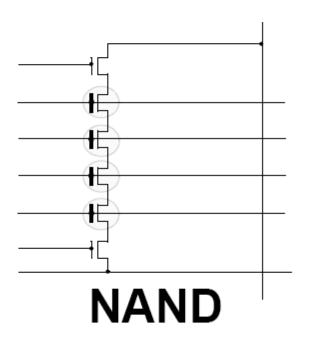

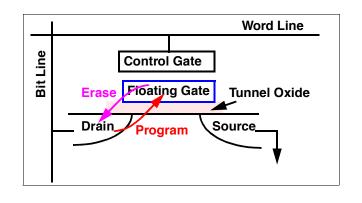

**Flash cell**

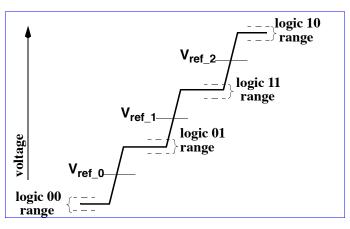

- Double gate where charge storage can be changed – control of the V<sub>th</sub> of the cell

- Cell Vth changes depending of the amount of F/G charge

- Electrons injected (ejected) into (out of) the F/G through Tox with electric field across Tox

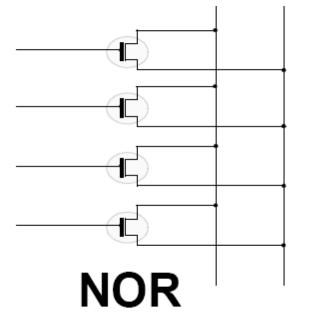

#### FLASH Technology

10x better endurance Fast read (~100 ns) Slow write (~10 μs) Used for Code Smaller cell size Slow read (~1 µs) Faster write (~1 µs) Used for Data

**Flash limitations**

- Limited number of write/erase (endurance)

- Necessary to generate high voltage (charge pump)

- Access time

- Integration ( > 10 masks)

- Scalability, charge retention lose on advanced nodes

- MLC Capabilities appreciated (but complex)

#### **Overall considerations**

- Bigger is slower

- Kbyte Mbyte → SRAM fast access time (~ns) low density (6T/cell) CMOS compatible easy to embed volatile

- Gbyte → DRAM reasonable access time (~ 30 ns) High density (2T/cell) Specific manufacture process – not easy to embed - volatile

- > 10 Gbyte → FIASH Slow access time (~ us) Very high density (1T/cell) Specific manufacture process – could be embed (> 10 masks) – non-volatile

- Faster is more expensive

- SRAM few \$ per Mbyte

- DRAM <1\$ per Mbyte

- FLASH < 1\$ per Gbyte

#### Other technologies have their place as well

#### • Currently used memories:

- SRAM for fast working memories

- Flash (data storage)

- FeRAM, smart cards

- • •

#### « Universal memory »candidates \_

- Magnetic tunneling junctions

- Phase change memory cells

- Programmable metallization cells

- OxRRAM

#### Universal memory:

"Non volatile RAM"

- Performance of SRAM

- •Cell size of DRAM/Flash

- •Non volatility of Flash

- Scalability

#### **Resistance Switching Memory**

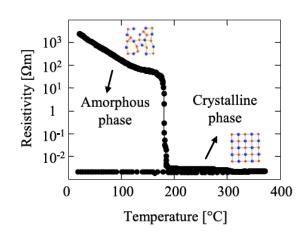

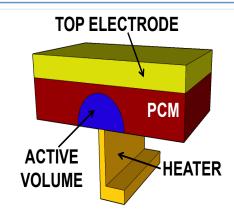

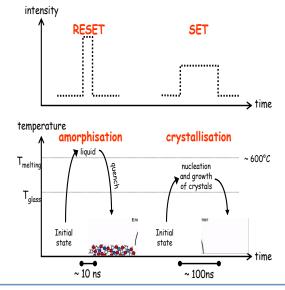

#### PCRAM Technology

Principe de fonctionnement : changement de phase du volume actif de l'élément de stockage de l'information

**ETAT SET** Phase cristalline

Lecture: contraste de résistance électrique entre la phase amorphe et la phase cristalline.

Ecriture: changement de phase induit par effet Joule sous l'application d'une impulsion électrique

#### PCRAM Technology

- Mémoire non-volatile (NVM)

- Temps d'accès court (12ns)

- Ecriture et effacement rapide (100ns)

- Tension de fonctionnement basse (3V)

- Ratio Roff/Ron important (x1000)

- Haute endurance (10<sup>12</sup> cycles)

- Rétention prouvée à 10 ans à 150°C y compris à température de soudage !

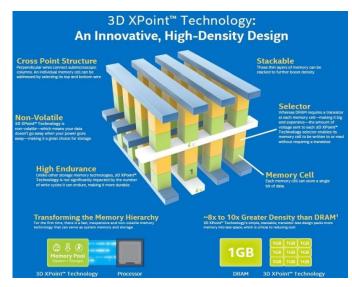

- Intégration 2D démontrée dans une architecture crossbar pour applications de stockage (cf. 3D XPoint)

- Technologie la plus mature parmi les candidates au remplacement de la flash (technologie industrielle)

## Défis

Dérive de résistance et courant de reset relativement haut affectent la mise à l'échelle de la cellule mémoire (élément de stockage et transistor de sélection)

From Intel / Micron websites

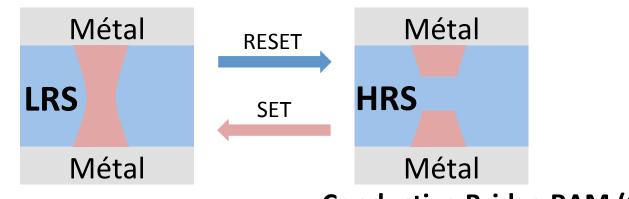

#### **ReRAM** Technology

Variation résistance d'une structure Métal\Isolant\Métal contrôlée électriquement

### 2 Etats

- HRS → Haute résistance (Etat « 0 »)

- LRS → Basse résistance (Etat « 1 »)

## 2 Opérations

- Set  $\rightarrow$  passage de l'état HRS à LRS

- Reset  $\rightarrow$  passage de l'état LRS à HRS

## Oxide-base RAM (OxRAM)

Filament conducteur = chaine de lacunes d'oxygène (migration)

#### **Conductive Bridge RAM (CBRAM)**

Filament conducteur = chaine d'atomes métalliques (Ag, Cu)

Switching filamentaire unidimensionnel dans les 2 cas

#### **ReRAM** Technology

#### **AVANTAGES**

- Structure simple, facile à fabriquer

- Fort potentiel pour la réduction de taille (mécanisme filamentaire)

- Faible tension (1V 3V)

- Courants de programmation 10-100 $\mu$ A

- Vitesse de commutation < 100ns

- Coût énergétique ~ 100pJ/bit

- Endurance > 10<sup>8</sup> cycles (OxRAM)

- Rétention de l'information > 10 ans à 70°C

- Intégration en BEOL à faible température mais aussi compatible FEOL (OxRAM)

- Des produits déjà démontrés

#### INCONVENIENTS

- Etape initiale de forming à plus haute tension pour créer le filament

- Variabilité importante de l'état HRS

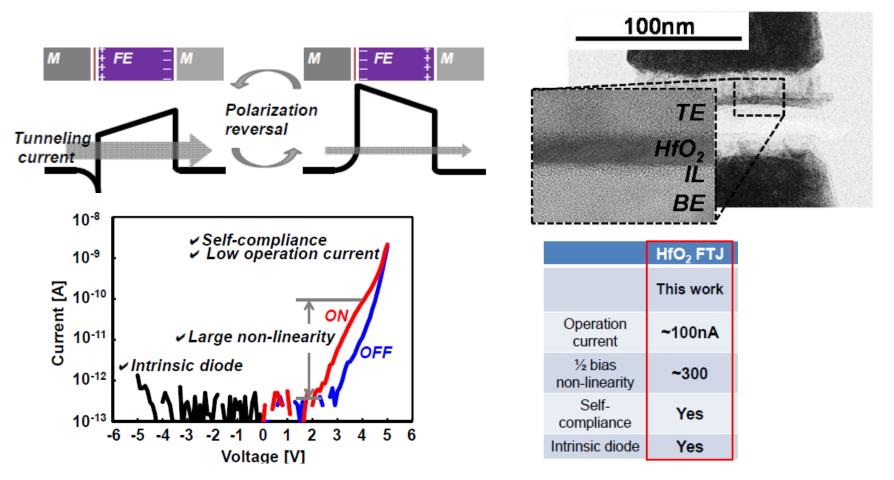

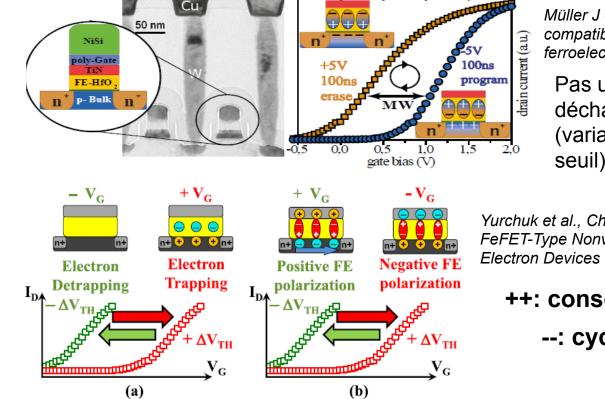

# Emerging Technologies : Fe-RAM

Shosuke F. et al., First demonstration and performance improvement of ferroelectric HfO2-based resistive switch with low operation current and intrinsic diode property, VLSI 2016

# Emerging Technologies : Fe-RAM

FE-HfO, based MFIS-Stack for 1T FRAM

Müller J et al. Ferroelectric hafnium oxide: a CMOScompatible and highly scalable approach to future ferroelectric memories. IEDM 2013

Pas un effet de chargement/ déchargement dans l'oxyde de grille (variation contraire de la tension de seuil)

Yurchuk et al., Charge-Trapping Phenomena in HfO2-Based FeFET-Type Nonvolatile Memories, IEEE Transaction on Electron Devices Vol. 63, No. 9, sept. 2016

- ++: consommation, rapidité

- --: cyclage, rétention

- Concept de mémoire non-volatile très récent, manque de maturité, démonstration d'intégration au nœud 28nm HKMG

- HfO2 ferroélectrique: utilisable aussi pour des transistors MOS à faible pente sous le seuil (concept de capacité négative de grille)

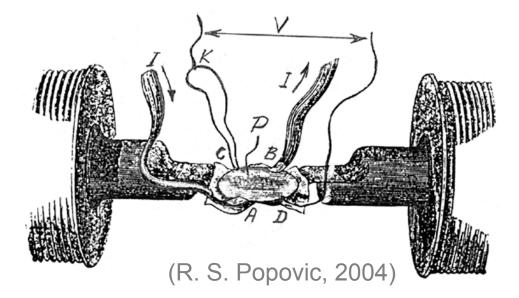

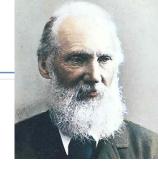

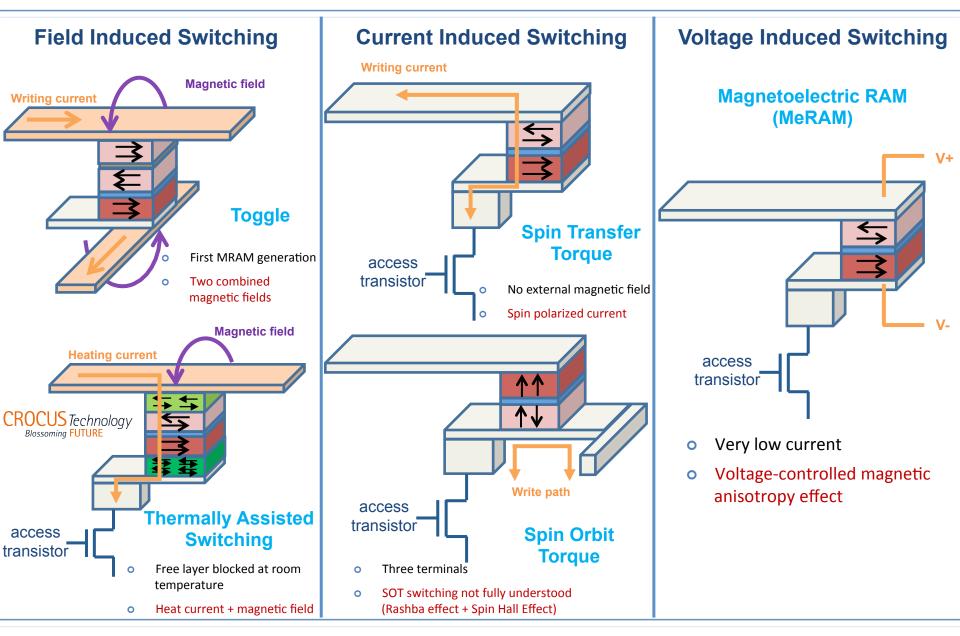

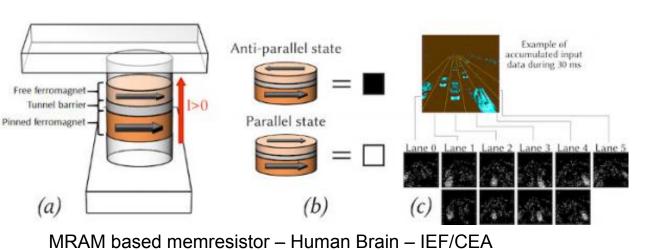

#### 3 – Emerging memory technologies : MRAM

Conductance of magnetic metal plates is larger in the presence of a magnetic field perpendicular to the current flow

William Thomson 1824-1907

- Currently known as Anisotropic Magnetoresistance (AMR)

- Resistance variation attained: 2%-5% in RT

#### 3 – Emerging memory technologies : MRAM

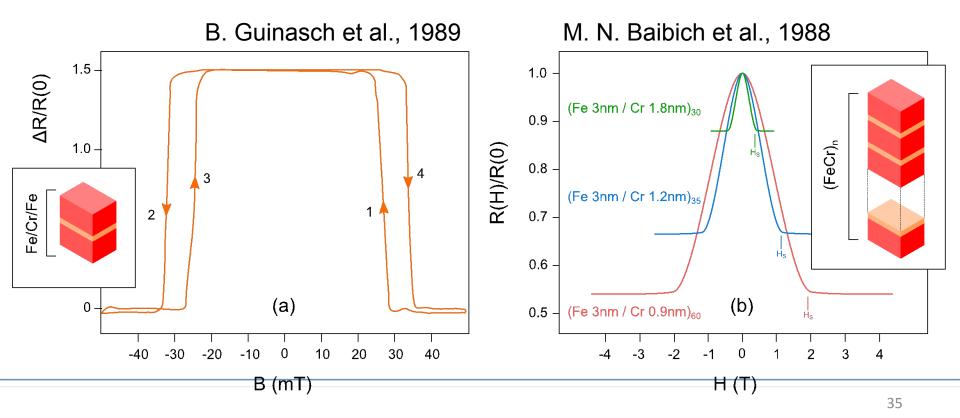

Peter Grünberg and Albert Fert 2007 Nobel Prize in Physics

Thin stacks of FM/NM metals have seen a conductance increase of up to 100% when subjected to a magnetic field

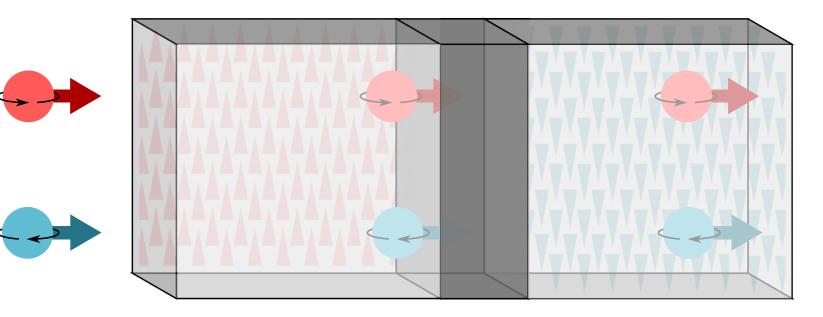

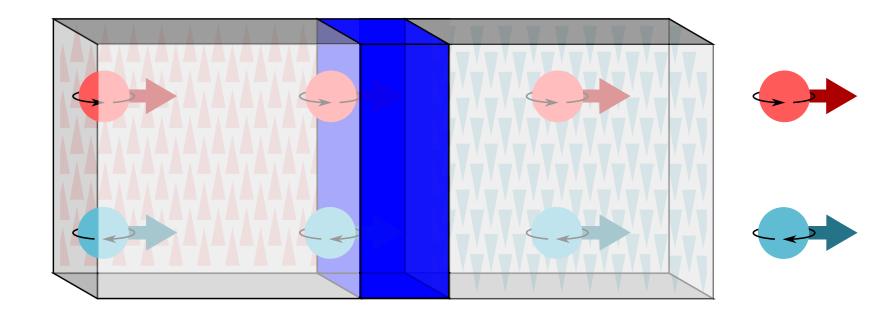

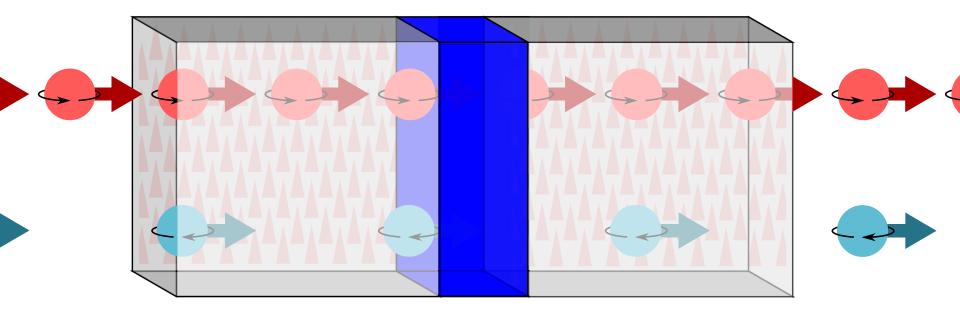

#### SPIN TECHNOLOGY OVERVIEW GIANT MAGNETORISTANCE

Peter Grünberg and Albert Fert 2007 Nobel Prize in Physics

**Anti-Parallel configuration**

• In FM/NM/FM structures, electrons are scattered as a result of interactions between the magnetic field and their spin

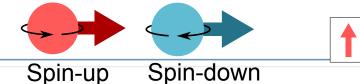

#### **SPIN TECHNOLOGY OVERVIEW GIANT MAGNETORISTANCE**

Peter Grünberg and Albert Fert 2007 Nobel Prize in Physics

In FM/NM/FM structures, electrons are scattered as a result of interactions between the magnetic field and their spin

T. Miyazaki, J. Moodera, J. Slonczewski (not in the pictures: M. Jullière)

Spin-up

• Spin-Dependent Transport (SDT): spin-up and spin-down have different probabilities of tunneling an FM/I/FM structure

T. Miyazaki, J. Moodera, J. Slonczewski (not in the pictures: M. Jullière)

• Spin-Dependent Transport (SDT): spin-up and spin-down have different probabilities of tunneling an FM/I/FM structure

Spin-up Spin-down

- Vitesse à l'écriture (~ns)

- Courant d'écriture ~5MA/cm<sup>2</sup> ⇔ 15uA pour 20nm, diminue avec la surface de la MTJ

- Endurance (>10<sup>14-15</sup>)

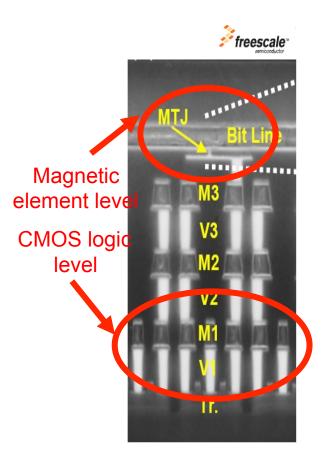

- Intégration sur CMOS

- Tension d'écriture et résistance (~kΩ) compatible avec CMOS

- ~3 masques supplémentaires

- Température back-end faible (<350°C)</li>

- Matériaux magnétiques « exotiques »

- Information non stockée sous forme de charge => immune aux radiations

- Compromis entre :

- Vitesse et consommation à l'écriture

- Rétention et consommation à l'écriture

- Scalabilité assurée jusqu'à 14 nm

- Stabilité proportionnelle au volume

- Courants d'écriture très petits : risque d'écriture lors de la lecture

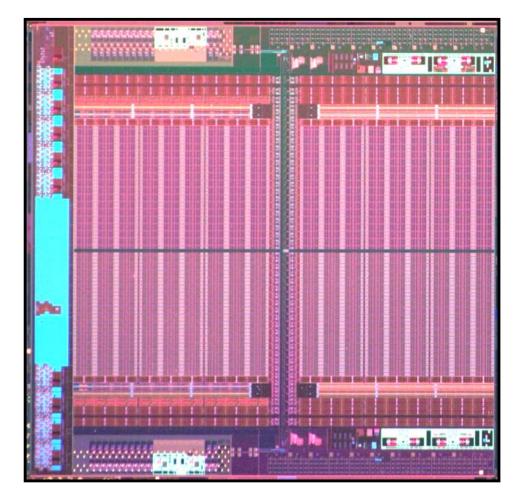

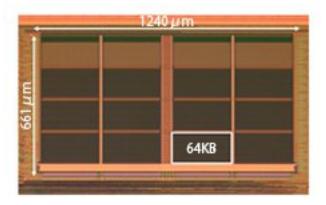

<STT-MRAM test chipt> STT-MRAM Cache memory

#### **Everspins MRAM Arduino Shield**

#### Crocus MRAM flexible sensors

### 3 – Emerging memory technologies : Overview

- All these technologies are Non-volatile, based on resistance switching, with fast access time

- Two important aspects to consider

- Technology maturity

- Système integration (easy to replace actual memory)

| Metricx     | PCM | OxRAM | CBRAM | PSTT MRAM | FeFET | Flash |

|-------------|-----|-------|-------|-----------|-------|-------|

| Endurance   | 4   | 4     | 2     | 5         | 1     | 3     |

| Energy      | 2   | 3     | 3     | 4         | 5     | 1     |

| Integration | 3   | 5     | 4     | 2         | 5     | 3     |

| Scalability | 4   | 5     | 5     | 4         | 3     | 1     |

| Retention   | 5   | 4     | 4     | 3         | 2     | 3     |

| Speed       | 4   | 3     | 3     | 5         | 4     | 1     |

| Maturité    | 3   | 3     | 2     | 2         | 1     | 5     |

### Techno overview summary

#### •J. Joshua Yang, Dmitri B. Strukov & Duncan R. Stewart Nature Nanotechnology 8, 13–24 (2013)

|                                      | Memristor        | PCM             | STTRAM           | SRAM                        | DRAM                                                    | Flash (NAND)    | HDD                    |  |

|--------------------------------------|------------------|-----------------|------------------|-----------------------------|---------------------------------------------------------|-----------------|------------------------|--|

|                                      |                  | Prototypes      |                  | Commercialized technologies |                                                         |                 |                        |  |

| Reciprocal density (F <sup>2</sup> ) | <4               | 4–16            | 20–60            | 140                         | 6–12                                                    | 14 <sup>†</sup> | 2/3                    |  |

| Energy per bit (pJ)                  | 0.1–3            | 2–25            | 0.1–2.5          | 0.0005                      | 0.005                                                   | 0.00002         | 1–10 × 10 <sup>9</sup> |  |

| Read time (ns)                       | <10              | 10–50           | 10–35            | 0.1–0.3                     | 10                                                      | 100,000         | 5–8 × 10 <sup>6</sup>  |  |

| Write time (ns)                      | ~10              | 50-500          | 10–90            | 0.1–0.3                     | 10                                                      | 100,000         | 5–8 × 10 <sup>6</sup>  |  |

| Retention                            | years            | years           | years            | As long as voltage applied  | < <second< td=""><td>years</td><td>years</td></second<> | years           | years                  |  |

| Endurance (cycles)                   | 10 <sup>12</sup> | 10 <sup>9</sup> | 10 <sup>15</sup> | >10 <sup>16</sup>           | >10 <sup>16</sup>                                       | 10 <sup>4</sup> | 10 <sup>4</sup>        |  |

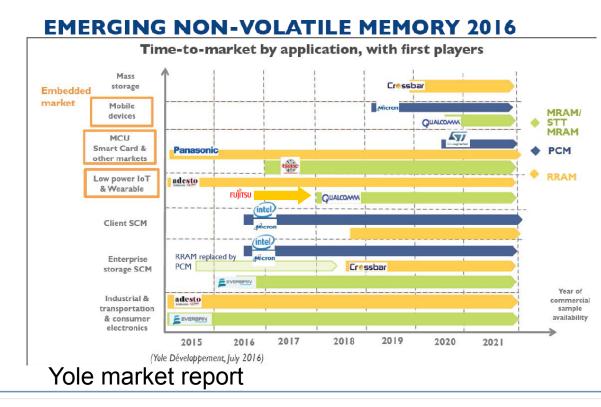

### 3 – Emerging memory technologies : Overview

- Actual market of emerging technologies is about 50 Millions \$ 80 billions for DRAM and Flash

- 2021: 4,6 billions \$, a market growth of 110% per year

- All the majors semiconductors companies are leading this market but lot of start-up too !

# Summary

- 1 Context and objectives of the lecture

- 2 Classical technologies and memory architecture overview (SRAM, DRAM, FLASH)

- 3 Emerging memory technologies

- 4 Computing with Non-Volatile memory technologies

- For high performance computing applications

- For Embedded applications (Non-volatile processor)

- For secure applications

- 5 Conclusions

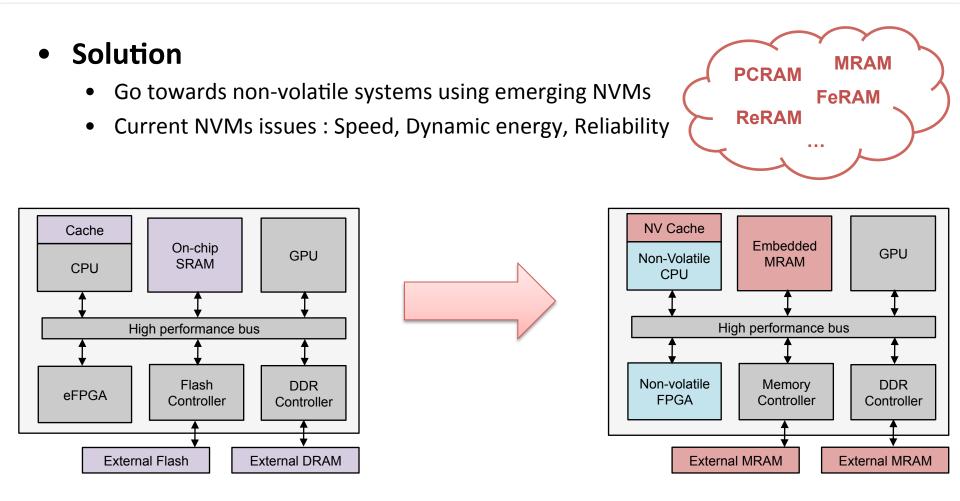

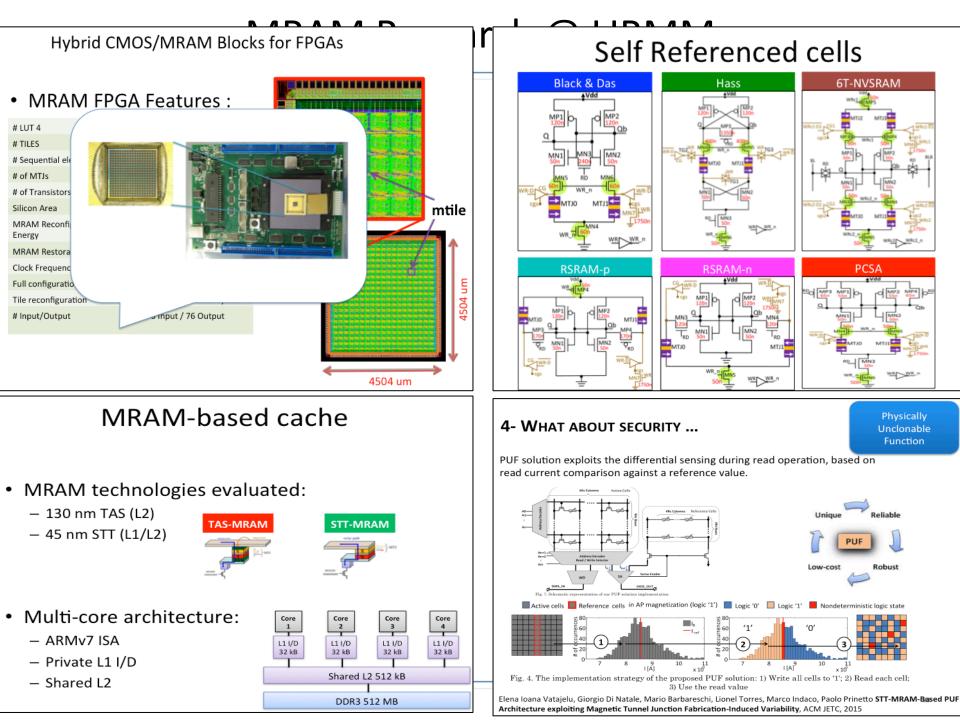

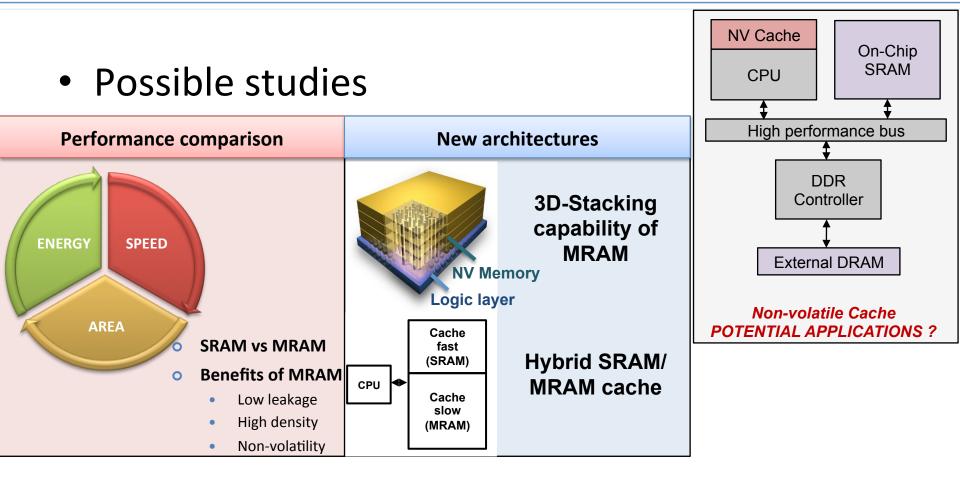

# Motivation

#### Where and how to place MRAM to:

reduce total power consumption ? keep same or get better performance ?

# Contributions

- 1. Evaluation of MRAM-based cache memory hierarchy:

- Exploration flow and extraction of memory activity

- L1 and L2 caches based on STT-MRAM and TAS-MRAM

- 2. Non-volatile computing

- *Instant-on/off* capability for embedded processor

- Analysis and validation of *Rollback* mechanism

- 3. Secure applications with NVM

#### Take advantages of MRAM

Low leakage High density Non-volatility

#### Mitigate drawbacks of MRAM

write latency write energy

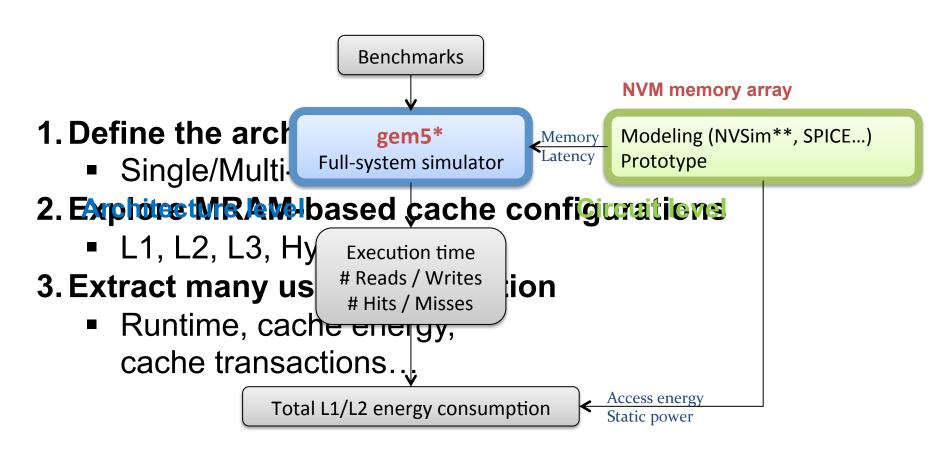

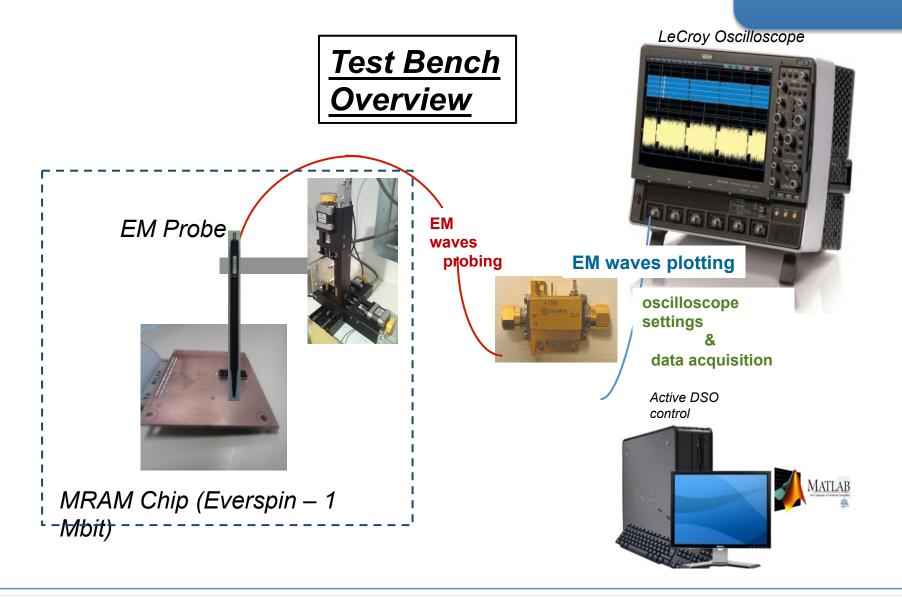

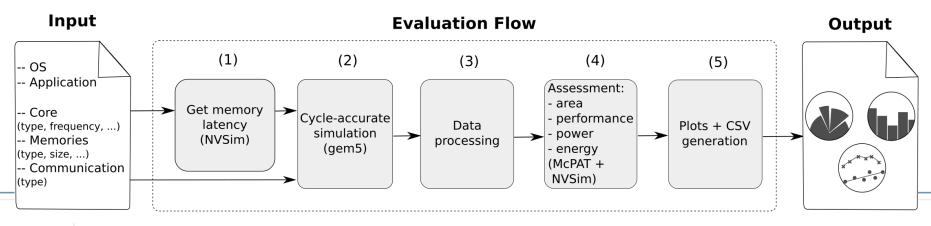

NVM exploration flow

\* N. Binkert et al., "The gem5 simulator," ACM SIGARCH Computer Architecture News, Aug. 2011.

\*\* X. Dong et al., "NVSim: A Circuit-Level Performance, Energy, and Area Model for Emerging Nonvolatile Memory," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Jul. 2012.

**Experimental setup**

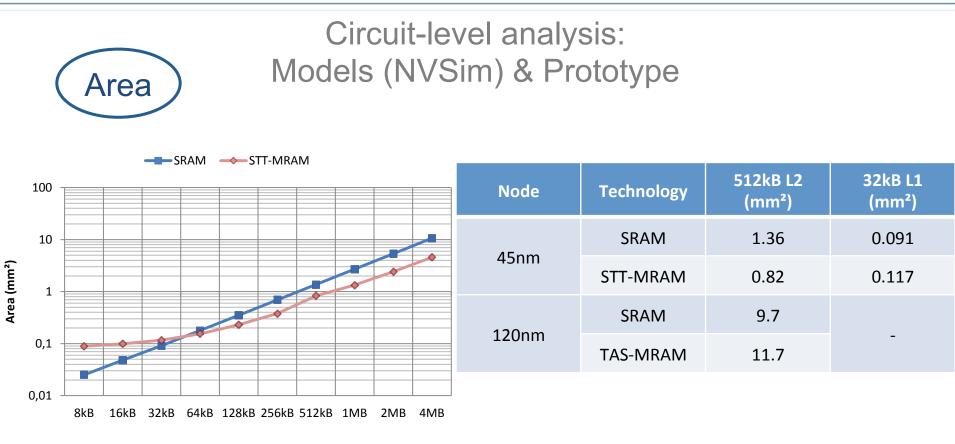

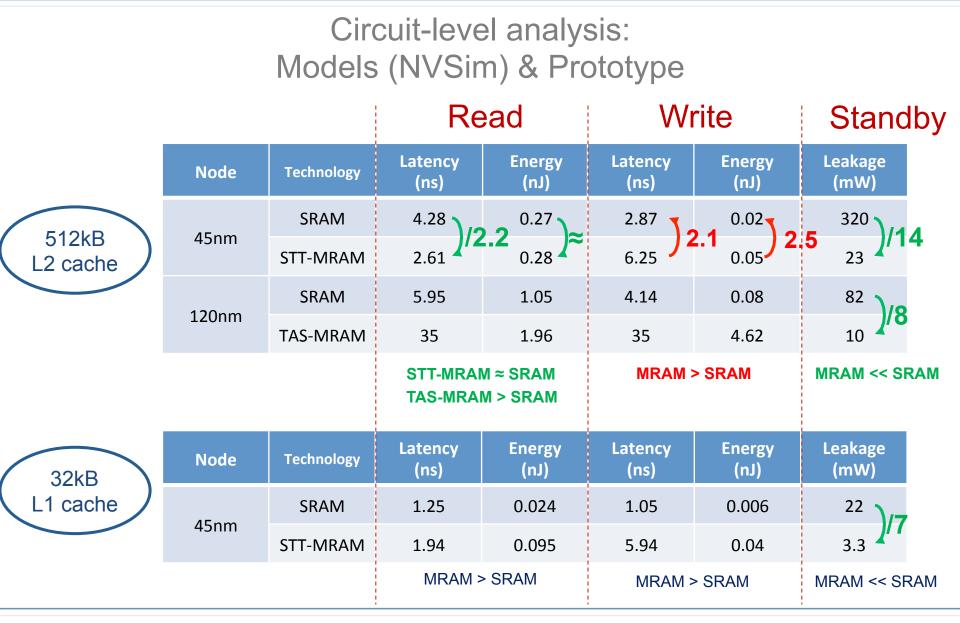

#### o MRAM is denser for large cache capacity

- MRAM cell size smaller than that of SRAM

- MRAM needs large transistors for write

- TAS-MRAM cache larger due to field lines

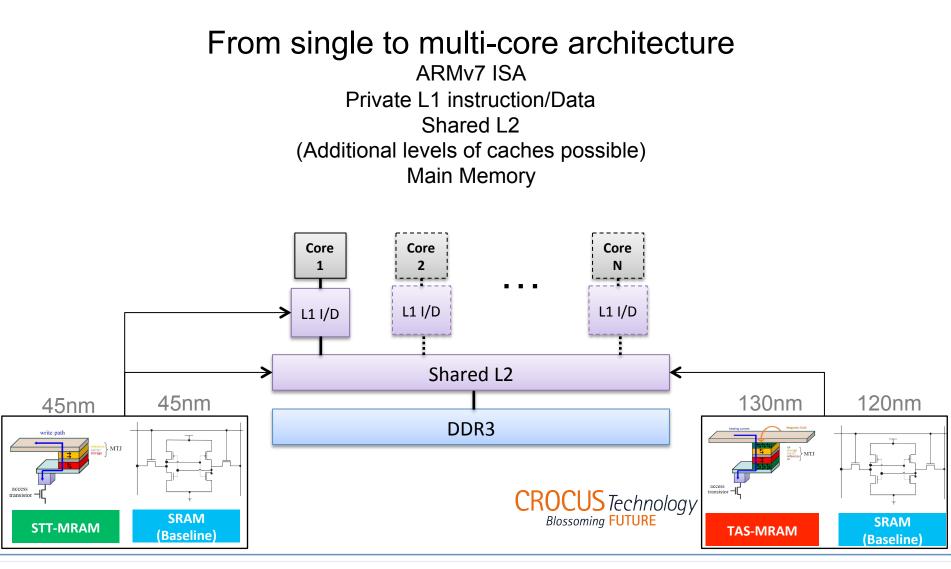

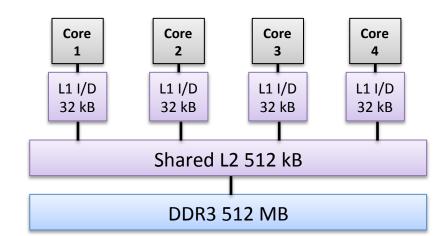

Case study

- Quad-core architecture:

- Frequency 1GHz

- ARMv7 ISA

- Private L1 I/D

- Shared L2

- DDR3 Main memory

- Benchmarks

- SPLASH-2

- Mostly high performance computing

- PARSEC

- Animation, data mining, computer vision, media processing

#### Architecture-level analysis: gem5

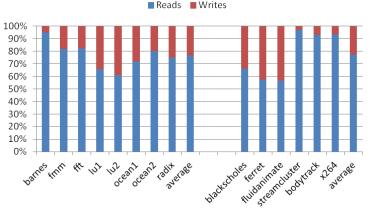

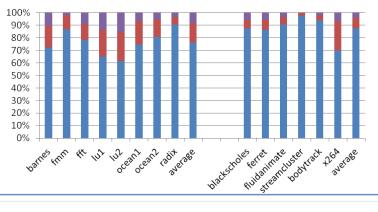

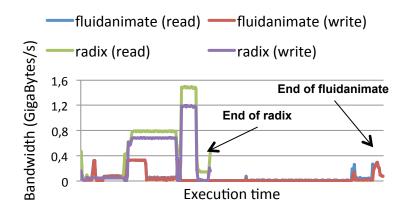

#### **Read/Write ratio**

ne reads 🛛 📕 I-Cache writes 🖉 D-Cache writes

#### L2/L1 access ratio

| Benchmark | Number of accesses                |              |  |

|-----------|-----------------------------------|--------------|--|

|           | L1 cache                          | L2 cache     |  |

| SPLASH-2  | ~2 billions<br>(0.5 billions/CPU) | ~26 millions |  |

| PARSEC    | ~12 billions<br>(3 billions /CPU) | ~16 millions |  |

#### Static/Dynamic energy ratio

Static energy

$L2 \rightarrow 90\%$  $L1 \rightarrow 80\%$

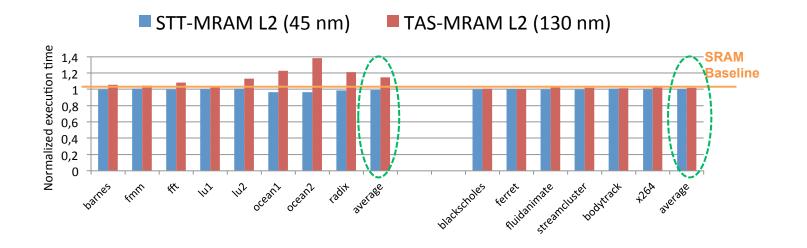

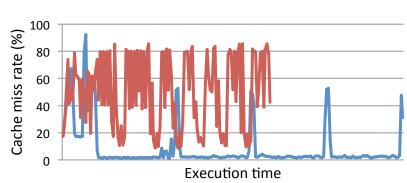

## MRAM-based L2

#### **Execution time**

- Observations:

- STT shows good performance

- L2 has small impact in overall performance

- For TAS, 14% of penalty in average (SPLASH-2)

- Depends on applications (Cache miss rate, L1/L2 access ratio)

(

ocean2

barnes

# MRAM-based L2

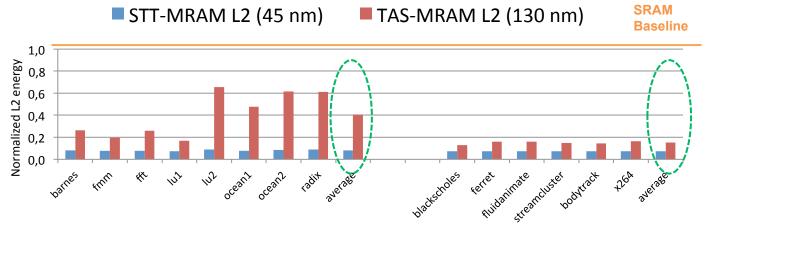

# Total L2 cache energy consumption

- Observations:

- Up to 90% of gain for STT

- From 40% to 90% for TAS

- Due to the very low leakage of MRAM-based cache

# MRAM-based cache

#### Summary

#### • NVM exploration flow available

- Input from models or silicon chip

- Memory activity analysis

#### • Is MRAM suitable for cache ?

- Good candidate for lower level of cache (L2 or last level cache)

- Up to 90% of energy gain

- No or small performance penalty

- More memory capacity using MRAM

- Cache L2 is up of 20% energy consumption of overall system

- Not suitable for upper level of cache (L1) for high performance but depending of the application some gain in energy

- Micro-architectural modifications required to mask latency

- Not detailed in this presentation but full evaluation of cache L1 done too

# Contributions

- 1. Evaluation of MRAM-based cache memory hierarchy:

- Exploration flow and extraction of memory activity

- L1 and L2 caches based on STT-MRAM and TAS-MRAM

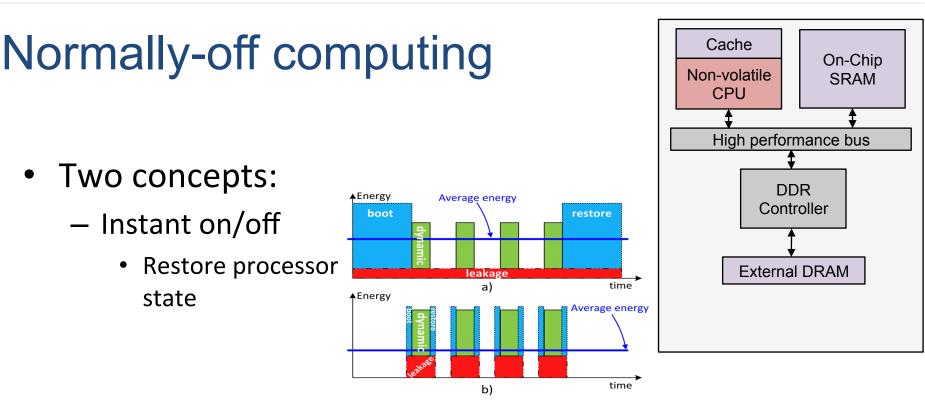

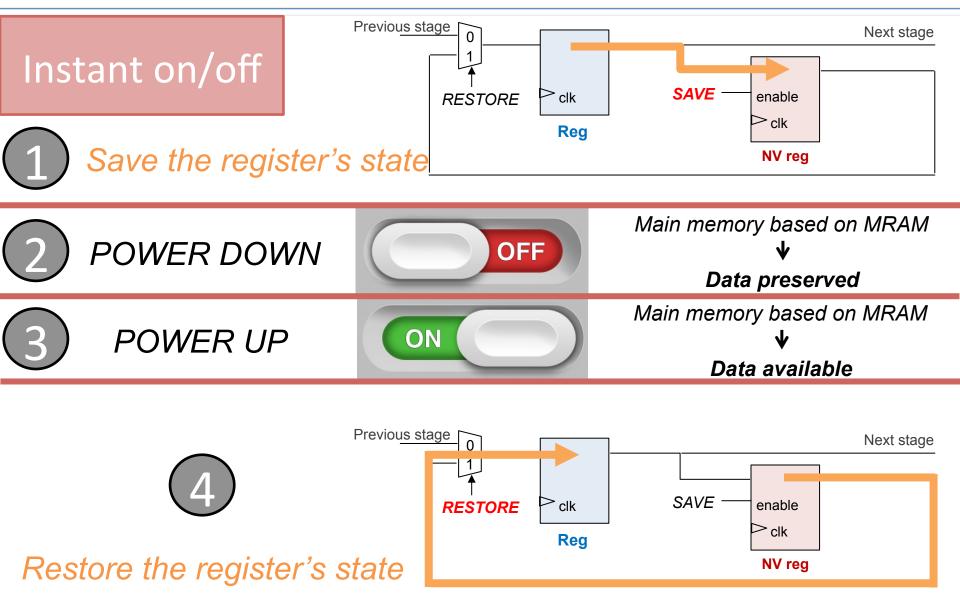

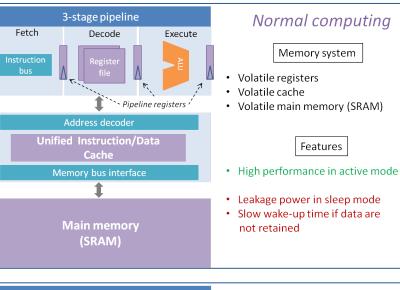

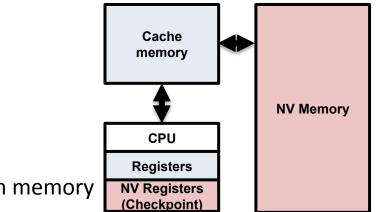

### 2. Non-volatile computing

- *Instant-on/off* capability for embedded processor

- Analysis and validation of *Rollback* mechanism

- 3. Secure applications with NVM

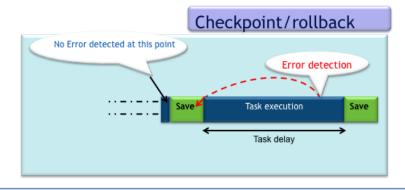

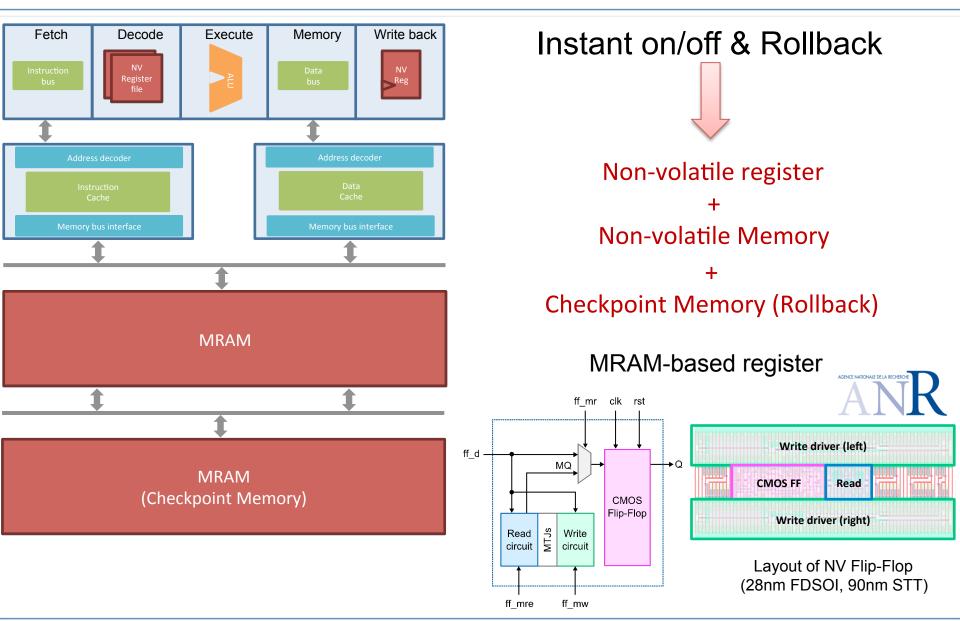

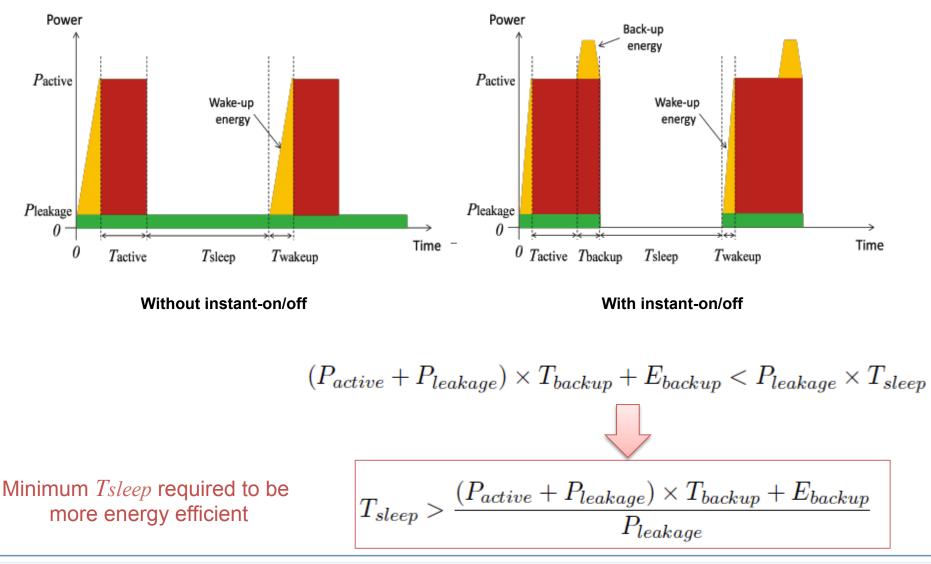

## **MRAM-based processor**

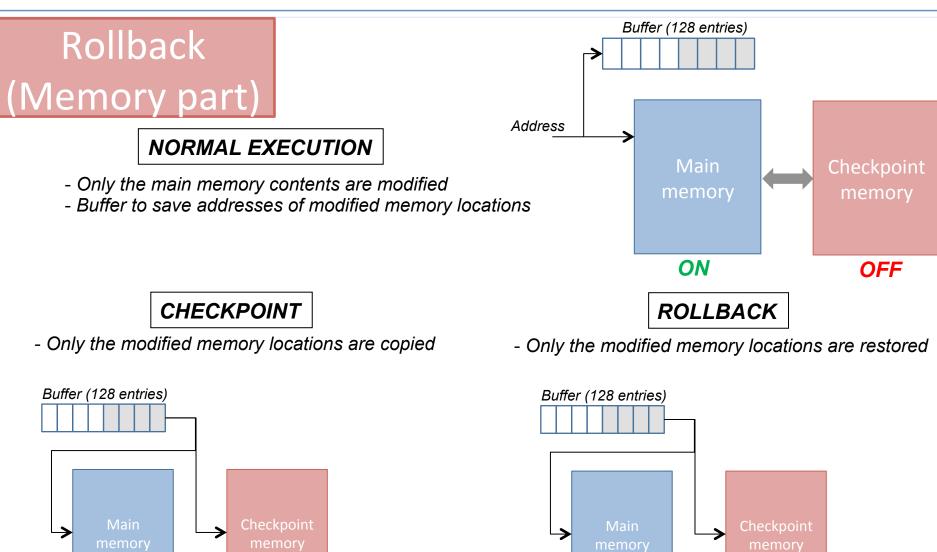

- Backward error recovery (Rollback)

- Restore previous valid state

## **MRAM-based processor**

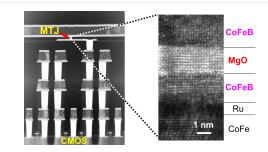

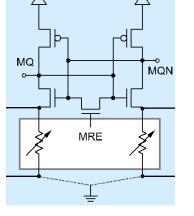

B. Jovanovic, R. Brum, L. Torres, *Comparative Analysis of MTJ/CMOS Hybrid Cells based* on TAS and In-plane STT Magnetic Tunnel Junctions, **IEEE Transactions on Magnetic**, 2014.

## **MRAM-based processor**

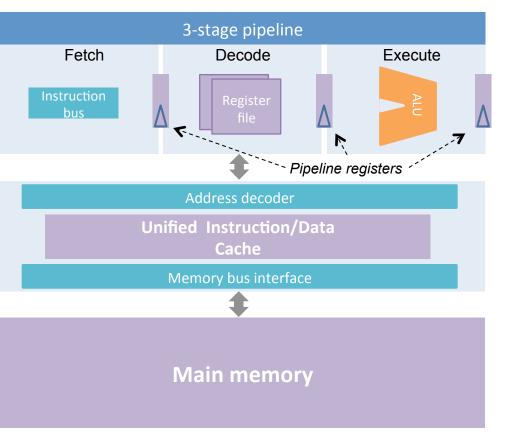

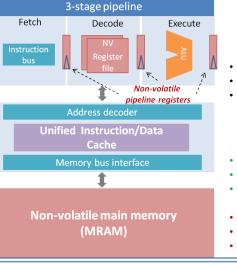

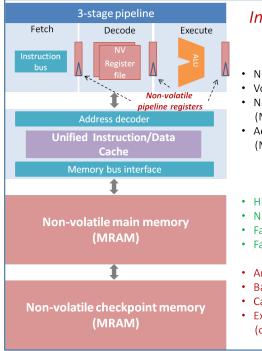

#### Case study: Amber 23 processor (ARM based instruction)

#### FEATURES

- 3-stage pipeline

- 16x32-bit register file

- 32-bit wishbone system bus

- Unified instruction/data cache (16 kBytes)

- Write through

- Read-miss replacement policy

- Main memory (> Mbytes)

- Multiply and multiply-accumulate operations

- Implementation of both instant-on/off and rollback (Verilog code modified)

- Duplication of the registers to emulate the non-volatility

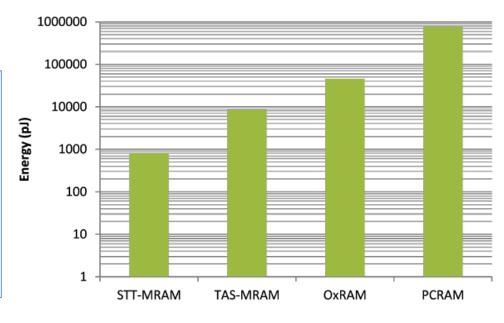

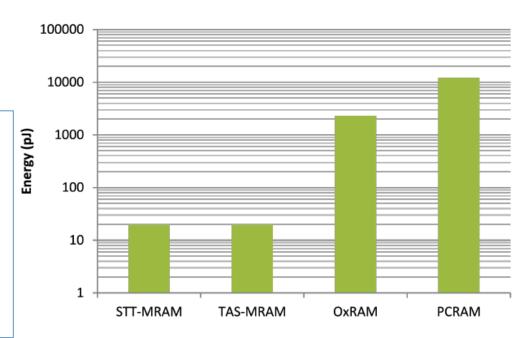

#### Instant-on/off: backup energy

Non-volatile flip-flops performance

| Technology                          | Latency (ns) Energy |         | gy (pJ) |         |

|-------------------------------------|---------------------|---------|---------|---------|

| rechnology                          | Restore             | Back-up | Restore | Back-up |

| STT-MRAM<br>[Chabi et al. 2014]     | 0.2                 | 4       | 0.012   | 0.5     |

| TAS-MRAM<br>[Jovanovic et al. 2015] | 0.13                | 16      | 0.012   | 5.2     |

| OxRAM<br>[Jovanović et al. 2014]    | 6                   | 70      | 1.4     | 28      |

| PCRAM<br>[Choi et al. 2013]         | 370                 | 370     | 7.4     | 463     |

• Backup energy:

- ightarrow less than 1nJ for STT-MRAM

- ightarrow less than 10nJ for TAS-MRAM

- [1] The required current to erase and program flash can vary from 4 to 12 mA

- 1644 Flip-Flops saved

- Flip-Flops are backed-up in parallel

[1] "Benchmarking mcu power consumption for ultra-low-power applications," White paper, Texas Instruments

#### Instant-on/off: Restore energy

| Non-volatile inp-nops performance   |         |         |             |         |  |

|-------------------------------------|---------|---------|-------------|---------|--|

| Technology                          | Laten   | cy (ns) | Energy (pJ) |         |  |

| reenhology                          | Restore | Back-up | Restore     | Back-up |  |

| STT-MRAM<br>[Chabi et al. 2014]     | 0.2     | 4       | 0.012       | 0.5     |  |

| TAS-MRAM<br>[Jovanovic et al. 2015] | 0.13    | 16      | 0.012       | 5.2     |  |

| OxRAM<br>[Jovanović et al. 2014]    | 6       | 70      | 1.4         | 28      |  |

| PCRAM<br>[Choi et al. 2013]         | 370     | 370     | 7.4         | 463     |  |

Non-volatile flip-flops performance

- Restore energy:

- $\rightarrow$  20pJ for both STT-MRAM and TAS-MRAM

- [1] Wang et al. showed that the energy consumption to restore 1607 Flip-Flops from off-chip flash (on-chip flash) is 1.3µJ (0.6µJ)

- 1644 Flip-Flops restored

- Flip-Flops are restored in parallel

[1] "A 3us wake-up time nonvolatile processor based on ferroelectric flip-flops," in ESSCIRC (ESSCIRC), Proceedings of the. IEEE, 2012

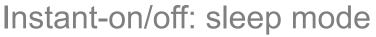

Instant-on/off: sleep mode

Switching activity  $\rightarrow$  0.5/cycle

Synthesis of the Amber 23 (65nm CMOS low-power HVT process)

$P_{active} = 173 \text{ mW} (40 \text{ MHz})$  $P_{leakage} = 12 \text{ mW}$

| Technology | Minimum <i>Tsleep</i> |

|------------|-----------------------|

| STT-MRAM   | 130 ns                |

| TAS-MRAM   | 968 ns                |

| OxRAM      | 4.9 μs                |

| PCRAM      | 69 µs                 |

- Not considering the power down/up circuitry

- Cache warm-up penalty to consider

- Area overhead to consider

ON

Restore

ON

Save

ON

ON

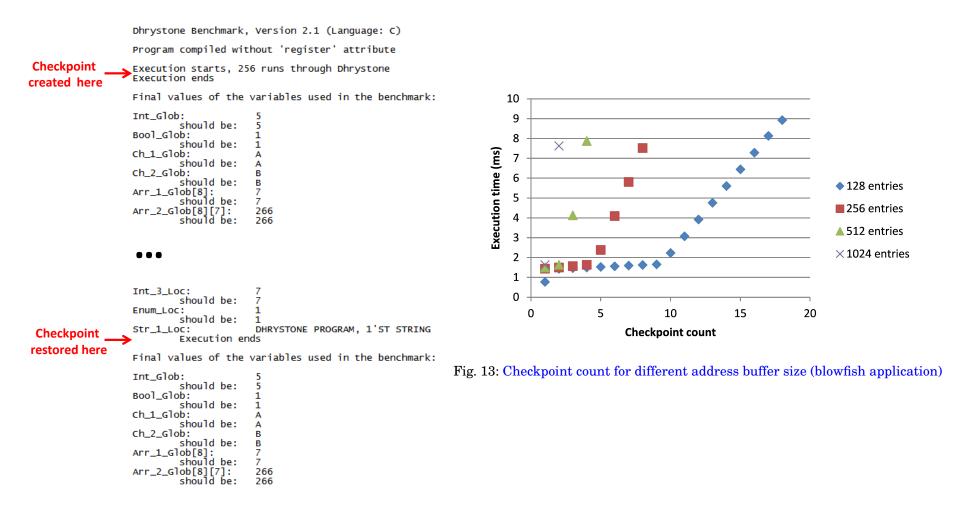

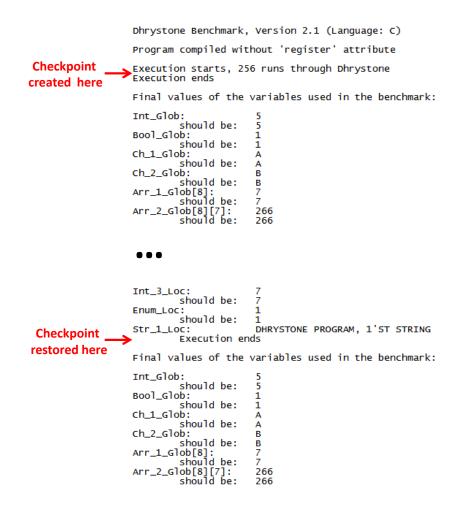

#### **Rollback: validation**

#### **Rollback: validation**

- Dhrystone 2.1 application

- Register part:

- Same time/energy as intant-on/ off to backup/restore

- Area overhead to consider

- Memory part:

- To be evaluated more precisely

- We know how to evaluate checkpoint memory size

- Penalty due to cache warm-up to consider

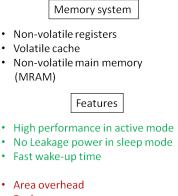

# Summary

#### Instant-on/off computing

#### Instant-on/off & Rollback Architectural changes

# Instant-on/off + Rollback Memory system Non-volatile registers Volatile cache Non-volatile main memory (MRAM) Additional checkpoint memory (MRAM)

#### • High performance in active mode

Features

- No Leakage power in sleep mode

- Fast wake-up time

- Fault tolerant (Rollback)

- Area overhead

- Back-up energy

- Cache warm-up

- Execution time penalty (checkpoints)

# Contributions

- 1. Evaluation of MRAM-based cache memory hierarchy:

- Exploration flow and extraction of memory activity

- L1 and L2 caches based on STT-MRAM and TAS-MRAM

- 2. Non-volatile computing

- *Instant-on/off* capability for embedded processor

- Analysis and validation of *Rollback* mechanism

- 3. Secure applications with NVM

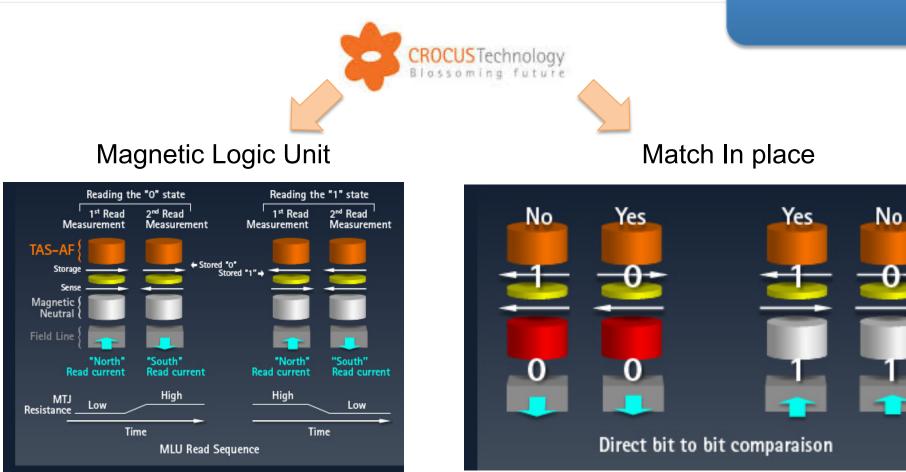

# Smart Efficient TRNG based on MRAM

Physically Unclonable Function using MRAM

Dedicated logic for secure Elements based on MRAM

Side Channel Analysis

Secure elements

Side Channel Analysis of MRAM memories

Fukushima & al (2015)

Vatajelu & al (2015)

True Number Generator

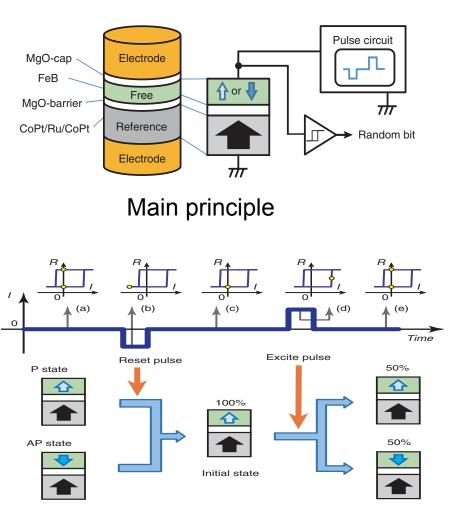

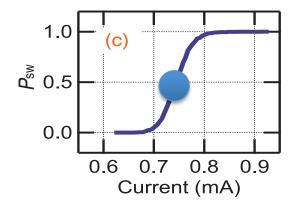

#### Smart Efficient TRNG based on perpendicular STT-MRAM

$$P_{\rm sw}(I) = 1 - \exp\left\{-\frac{t}{\tau_0} \exp\left[-\Delta\left(1 - \frac{I}{I_{\rm c0}}\right)^2\right]\right\},\qquad(1)$$

Table II.

Pass rate of the randomness tests of NIST SP-800.<sup>18)</sup>

|      | Pass rate |       |                  |                  |

|------|-----------|-------|------------------|------------------|

|      | Raw       | XOR   | XOR <sup>2</sup> | XOR <sup>3</sup> |

| MTJ1 | 0.000     | 0.000 | - 0.417          | - 0.467          |

| MTJ2 | 0.000     |       |                  |                  |

| MTJ3 | 0.000     | 0.167 |                  |                  |

| MTJ4 | 0.000     |       |                  |                  |

| MTJ5 | 0.000     | 0.058 | - 0.475          |                  |

| MTJ6 | 0.000     |       |                  |                  |

| MTJ7 | 0.000     | 0.075 |                  |                  |

| MTJ8 | 0.000     |       |                  |                  |

Akio Fukushima\*, Takayuki Seki, Kay Yakushiji, Hitoshi Kubota, Hiroshi Imamura, Shinji Yuasa, and Koji Ando Spin dice: A scalable truly random number generator based on spintronics, Applied Physics Express **7**, 083001 (2014)

True Number Generator

15

Smart Efficient TRNG based on perpendicular STT-MRAM (instead current pulse, external field is used) 50

TRNG MRAM source 1 Random number Threshold = Raw sequence mean = 0.2464 MRAM Converted sequence mean = 0.51165 source 2 **TRNG** Output Correction **XORed** sequence MRAM 1 2 3 5 6 7 10 11 12 4 8 9 13 14 source n Initial Von N. Parity 5th Parity 7th Parity 9th

Experiment done with IEF, Thibault DEVOLDER

**NIST Test**

50 Millions of random bits

- Non-Volatility help security (and also Energy !)

- Persistent data storage

- Authentication

- Battery backed-memories

- Secure CPU Boot

NV – SRAM 2 NV state 1 Volatile State

B. Jovanovic, R. Brum, L. Torres, *Comparative Analysis of MTJ/CMOS Hybrid Cells based on TAS and In-plane STT Magnetic Tunnel Junctions*, **IEEE Transactions on Magnetic**,

Secure elements

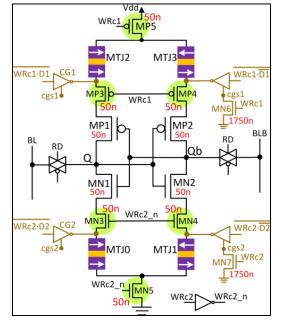

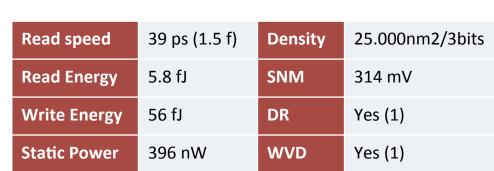

Non-Volatile SRAM/MRAM cel

#### Secure elements

- Non-Volatility help security (and also Energy !)

- Persistent data storage

- Authentication

- Battery backed-memories

- Secure CPU Boot

- ....

Non-Volatile SRAM/MRAM cell

- First evaluation of NV CPU @ LIRMM :

- 32-bit RISC like processor

- Validation of checkpoint/rollback capability

- Non-Volatile register bank (instead Volatile)

- Low performance overhead

- Non-volatile memory from register level to main memory

B. Jovanovic, R. Brum, L. Torres, *Comparative Analysis of MTJ/CMOS Hybrid Cells based on TAS* and *In-plane STT Magnetic Tunnel Junctions*, **IEEE Transactions on Magnetic**,

Secure elements

**XOR** Function

#### Authentication function/comparison

Symetric Cryptography  $\rightarrow$  Elementary operations XOR, Substitution, Shift

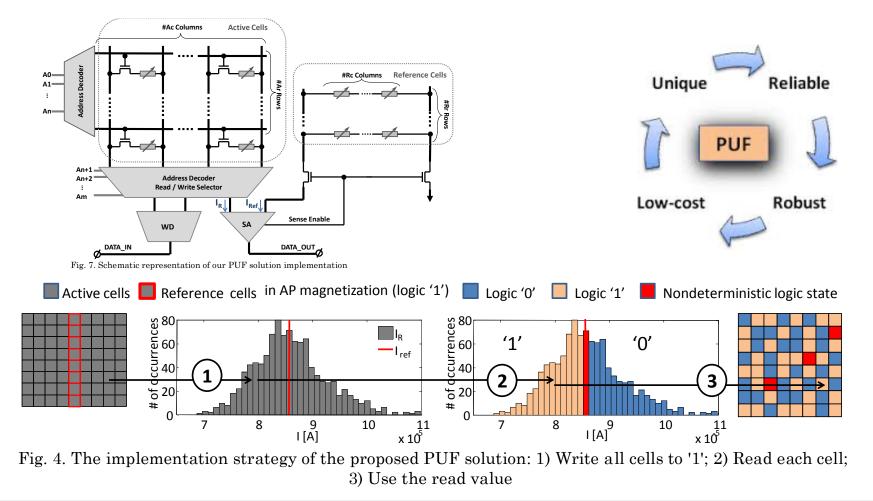

Physically Unclonable Function

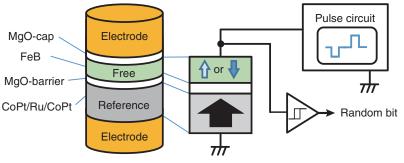

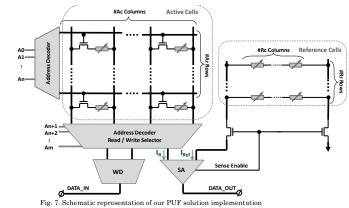

PUF solution exploits the differential sensing during read operation, based on read current comparison against a reference value.

Elena Ioana Vatajelu, Giorgio Di Natale, Mario Barbareschi, Lionel Torres, Marco Indaco, Paolo Prinetto STT-MRAM-Based PUF Architecture exploiting Magnetic Tunnel Junction Fabrication-Induced Variability, ACM JETC, 2015 81

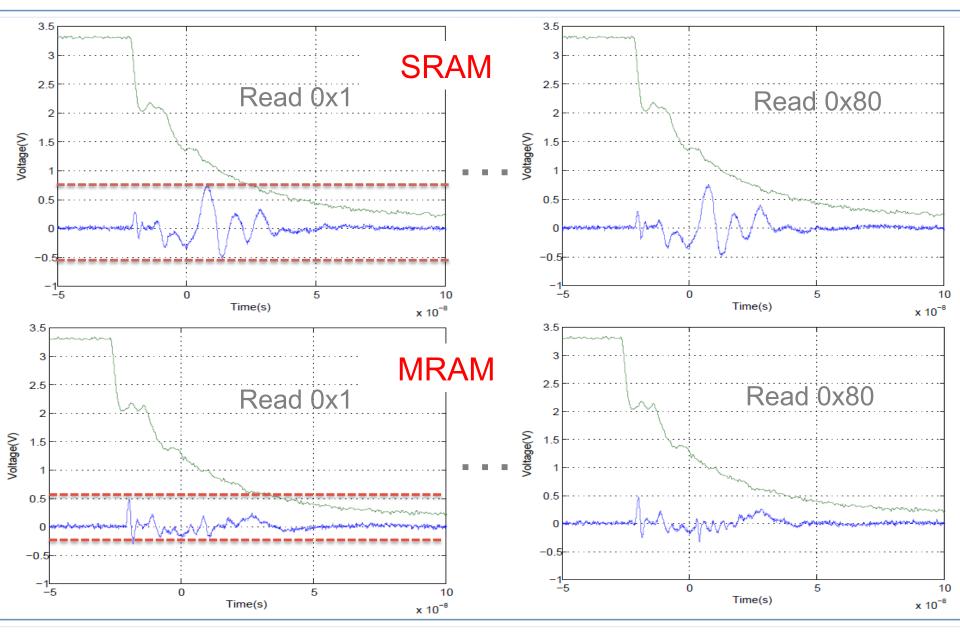

#### Side Channel Analysis

# **MRAM Conclusion**

MRAM has a high potential to:

- Certainly Reduce energy consumption

- At cache level (sure and proven)

- Normally-off computing (to be confirmed)

- Can facilitate some features

- Normally-off computing / Instant on-off

- Backward error recovery (Rollback)

- Results should be confirmed through measurements on silicon prototype !

- Link with compilation and OS ( $\rightarrow$  National project started, Non-volatility )

- Under development : a complete flow including power consumption estimation of processor + memory hierarchy

# **Overall Conclusion**

- No Ideal memory technology really depending of the targeted application

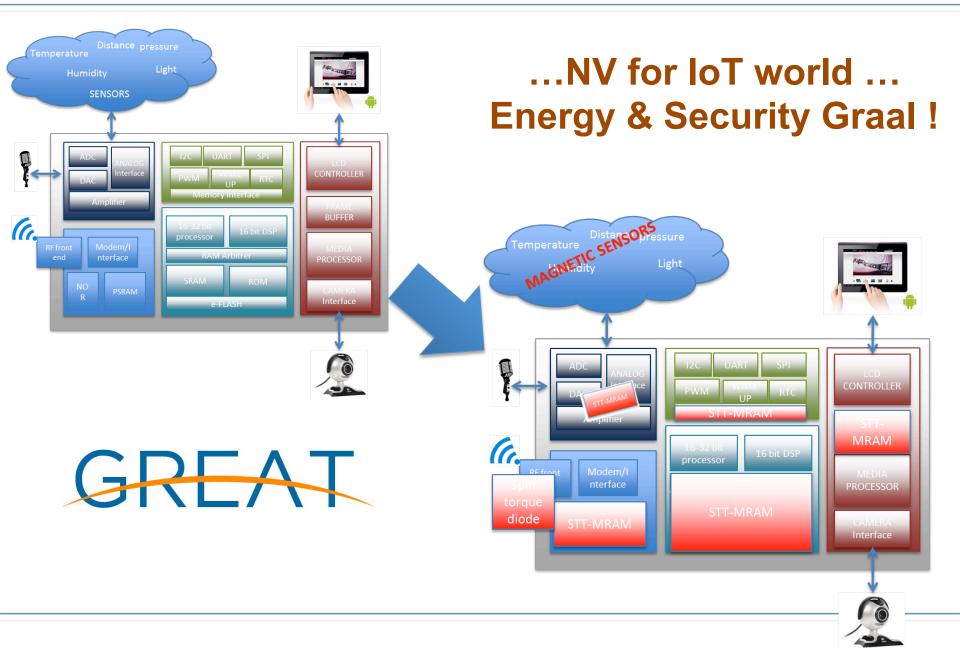

- Normally-off computing will be tomorrow the key element for SoC design (for Energy !)

- But Non-Volatile memory could change the way to imagine the memory hierarchy

- Rather than improved the memory hierarchy... rethink it!

- Distributed NV elements/memories

- Security (with IoT trend) will be everywhere

- Better understand NV technologies for security issues

- Use NV Technologies for security !

# NV future ...

# THANK YOU FOR YOUR ATTENTION

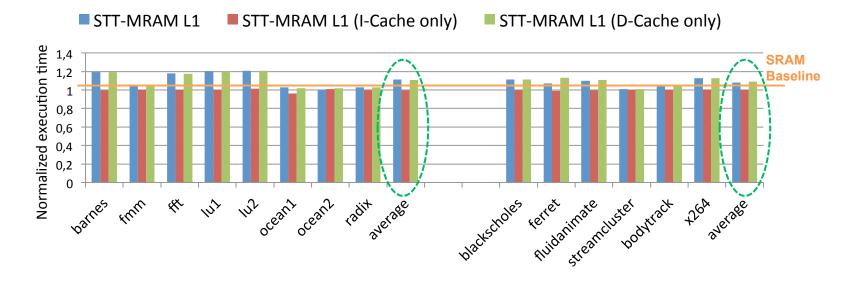

# MRAM-based L1

### **Execution time**

- Observations:

- Up to 21% of runtime penalty

- L1 much more accessed than L2

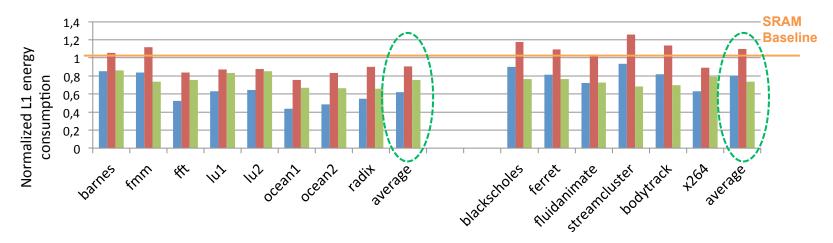

# MRAM-based L1

## **Total L1 energy consumption**

STT-MRAM L1 STT-MRAM L1 (I-Cache only) STT-MRAM L1 (D-Cache only)

- Observations:

- Low leakage does not always compensate the high dynamic energy of MRAM