# Thinking and Designing Differently: The Asynchronous Alternative

Laurent Fesquet

Grenoble Institute of Technology

**TIMA** laboratory

#### Outline

- **Designing synchronous circuits**

- Asynchronous circuit principles

- Asynchronous circuit design principles

- Asynchronous circuit classes

- Exploiting the asynchronous logic

- Success stories

- conclusion

#### Outline

- Designing synchronous circuits

- Asynchronous circuit principles

- Asynchronous circuit design principles

- Asynchronous circuit classes

- Exploiting the asynchronous logic

- Success stories

- conclusion

Synchronous circuit model

Speaker: Laurent Fesquet

Date: March 25, 2013

Page: 4

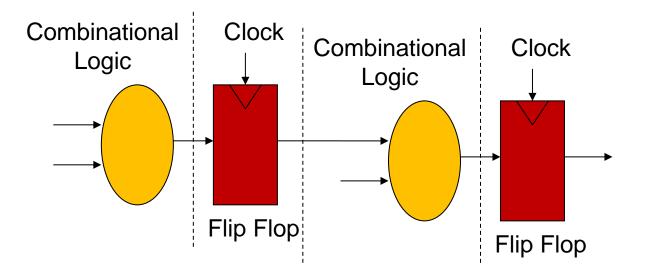

Synchronous circuit model

© Speaker: Date: Page:

Laurent Fesquet March 25, 2013 5

Grenoble INP

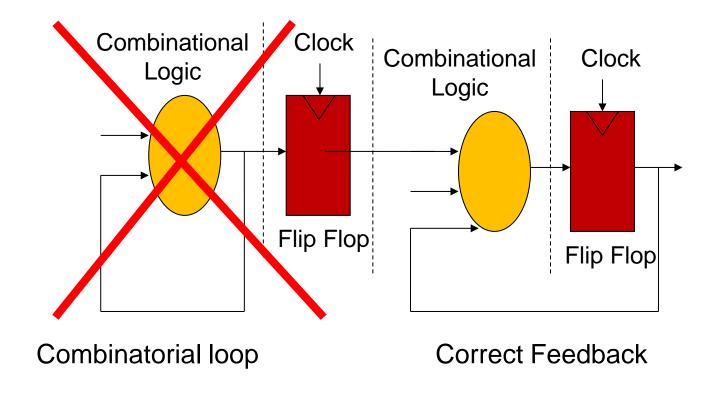

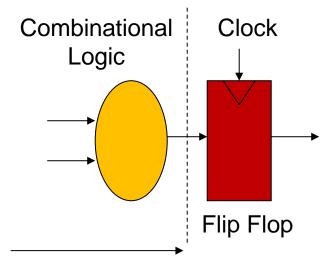

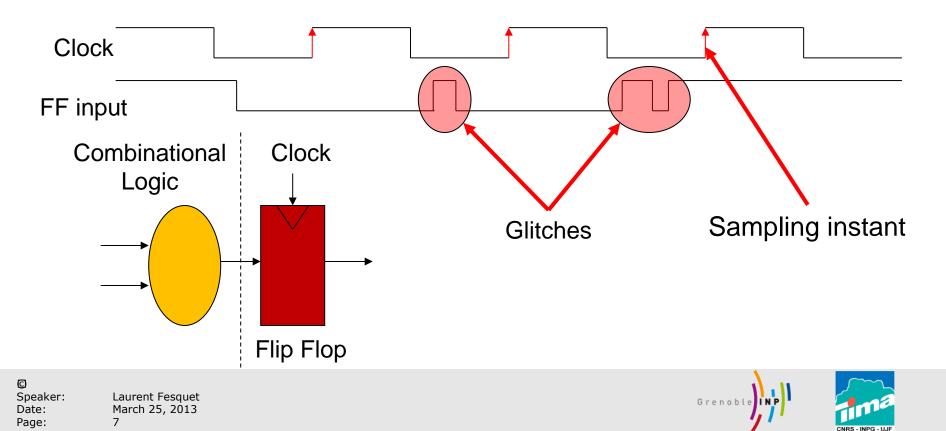

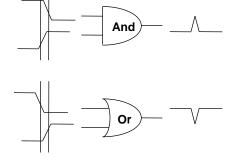

Synchronous circuits use timing assumptions

**Critical path** = Longuest path (worst case)

#### Correct behavior when Tcritical < Tclock</li>

© Speaker: Date: Page:

Laurent Fesquet March 25, 2013 6

- Hazard is allowed (before sampling)

- Combinatorial logic is stable before sampling

Thinking and Designing Differently: The Asynchronous Alternative

#### Outline

- **Designing synchronous circuits**

- **Asynchronous circuit principles**

- Asynchronous circuit design principles

- **Asynchronous circuit classes**

- Exploiting the asynchronous logic

- Success stories

- conclusion

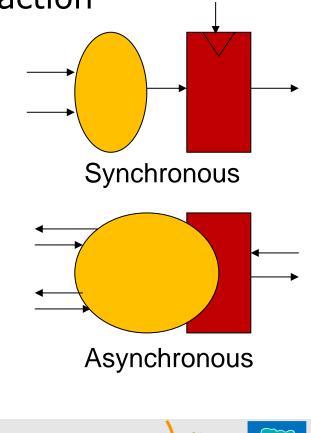

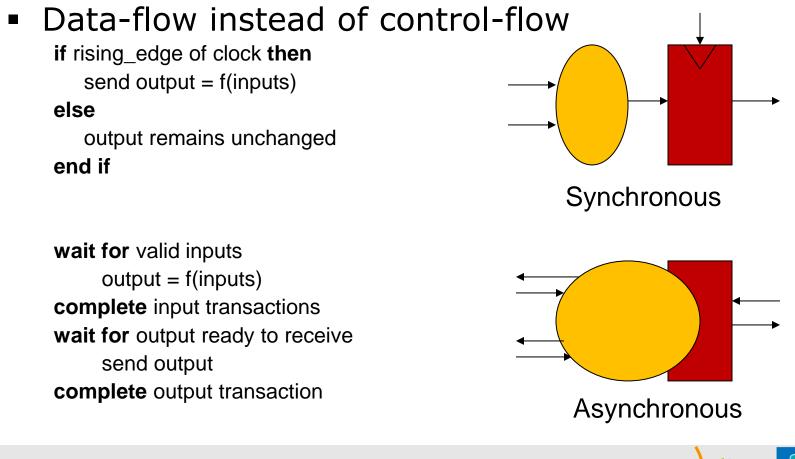

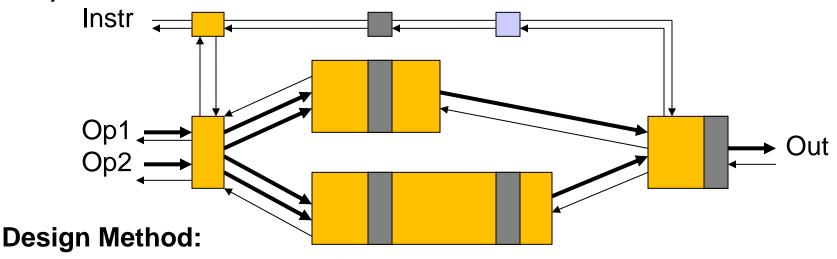

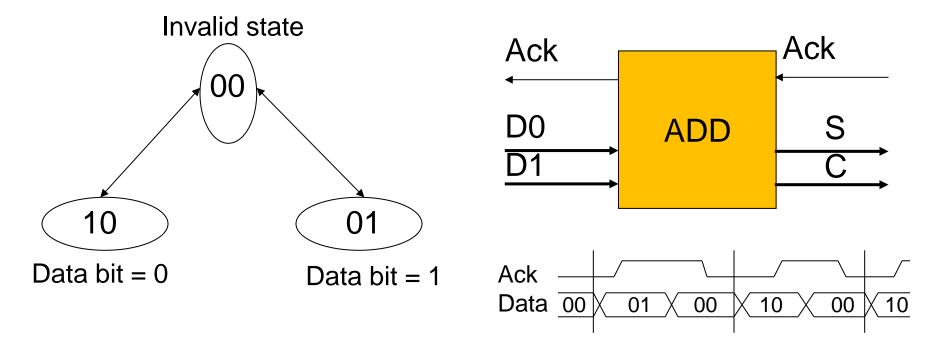

At the hardware module abstraction

Every rising edge clock triggers the computation

Data availability triggers the computation

- → Global Clock is *replaced*

- $\rightarrow$  by **local channels** (handshaking)

Speaker: Laurent Fesquet Date: March 25, 2013 Page: 9

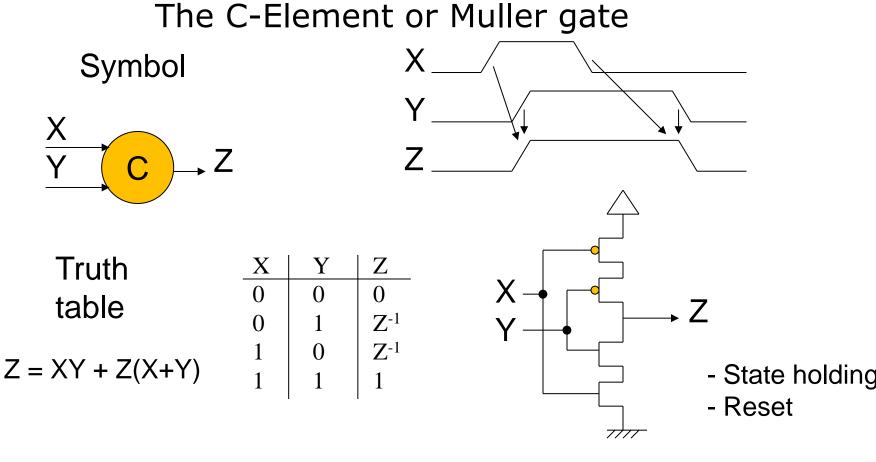

C

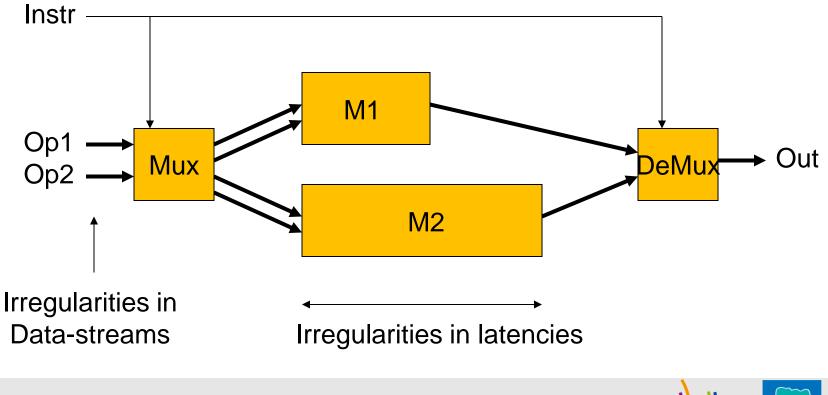

Composing hardware modules

Laurent Fesquet March 25, 2013

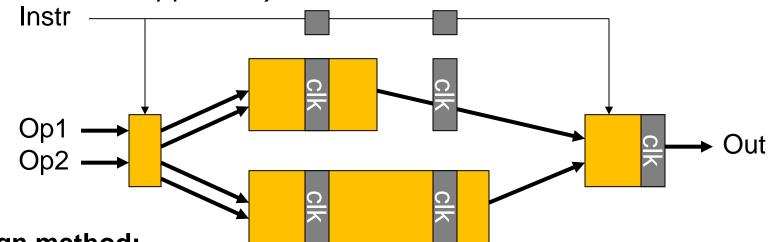

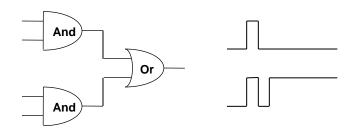

Synchronous circuits : balance the pipelines (worst case approach)

#### **Design method:**

Need to know the state of the whole architecture at each cycle

- $\rightarrow$  What happen if the system is very complex ?

- $\rightarrow$  Difficult to exploit input data stream irregularities

- $\rightarrow$  Circuit: add latency, increase power consumption

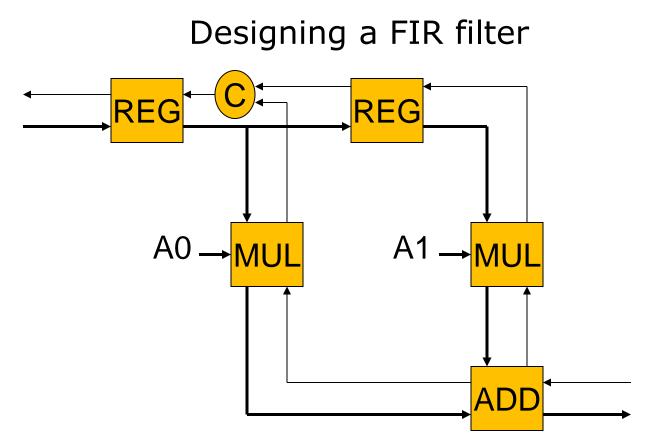

Asynchronous circuits : ensure data flows

No need to know the state of the architecture pipelining preserves the functional correctness

→Circuit: latency is always minimum, as well as power consumption

→Easy to compose a complex system using simple modules

→Free to exploit input data stream irregularities

© Speaker: Lau Date: Mai Page: 13

Laurent Fesquet March 25, 2013 13 renoble INP

## Outline

- Designing synchronous circuits

- Asynchronous circuit principles

- Asynchronous circuit design principles

- Asynchronous circuit classes

- Exploiting the asynchronous logic

- Success stories

- conclusion

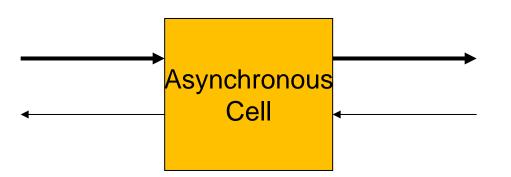

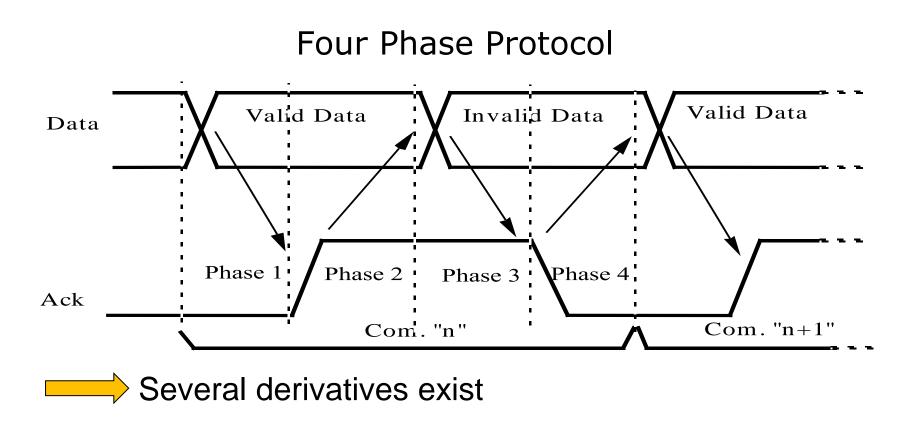

# A basic asynchronous cell

- Bit level

- Arithmetic function

- Complex function

- Maximal speed: minimal forward latency

- Maximal throughput: minimal cycle time

- Respect the handshake protocol

#### **Design issues locally solved** cells are easy to reuse

© Speaker: Laurent Fesquet Date: March 25, 2013 Page: 17

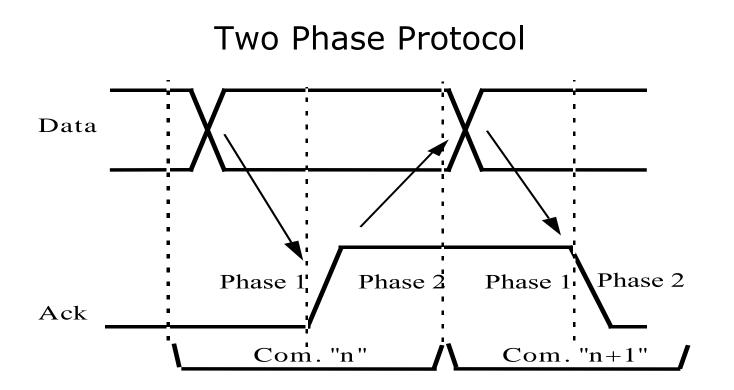

- Protocol

- Two phases

- Four phases

- Signaling

- Data encoding / Request

- Three states

- Four states

- Acknowledge

© Speaker: Laurent Fesquet Date: March 25, 2013 Page: 20

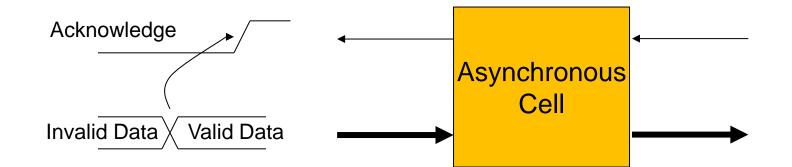

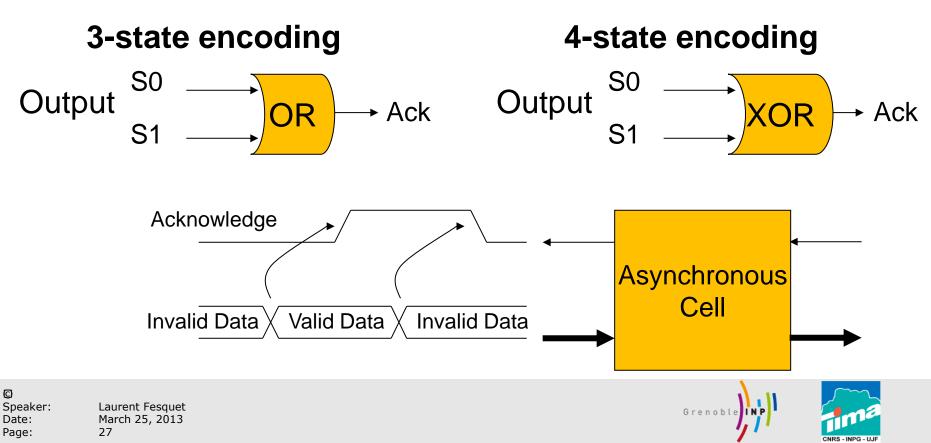

- 3-state encoding

- Data Valid/Invalid Signaling

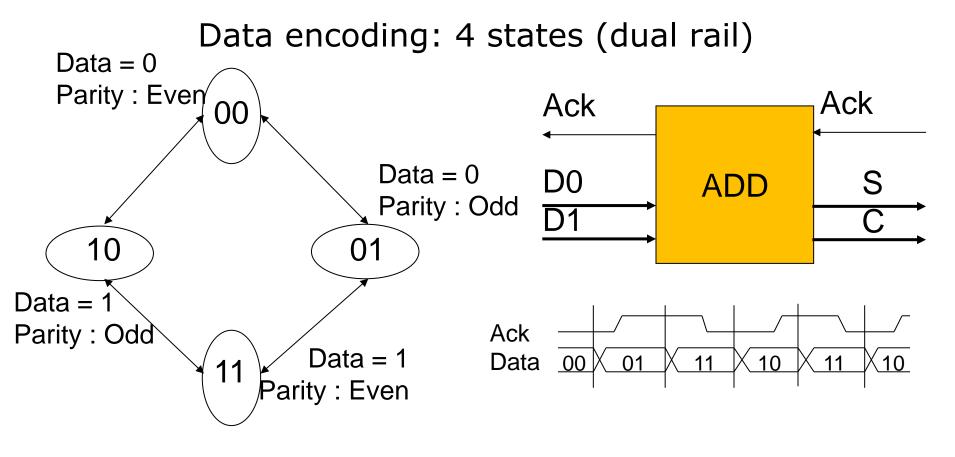

- 4-state encoding

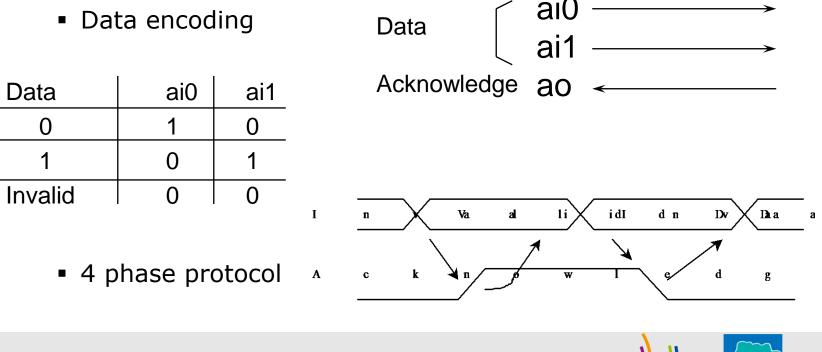

#### Data encoding: 3 states (dual rail)

© Speaker: Laurent Fesquet Date: March 25, 2013 Page: 22

Grenoble

© Speaker: Laurent Fesquet Date: March 25, 2013 Page: 23

Grenoble

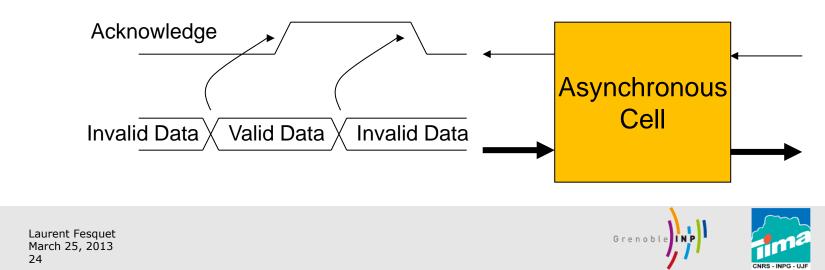

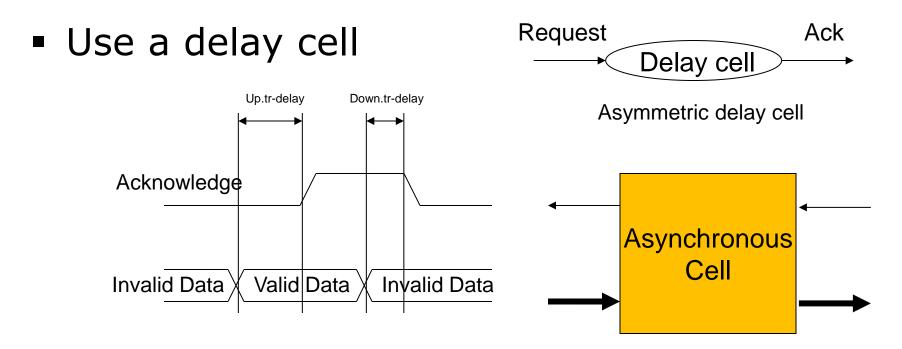

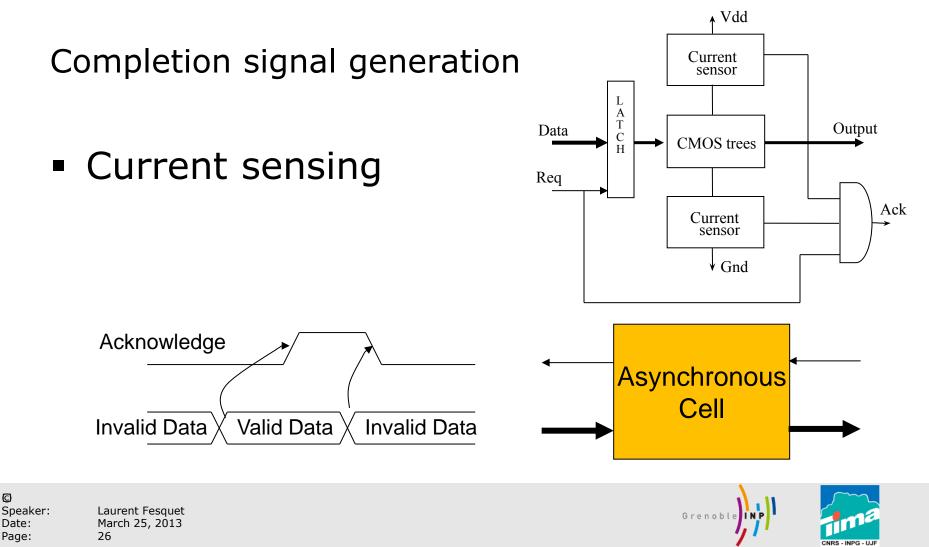

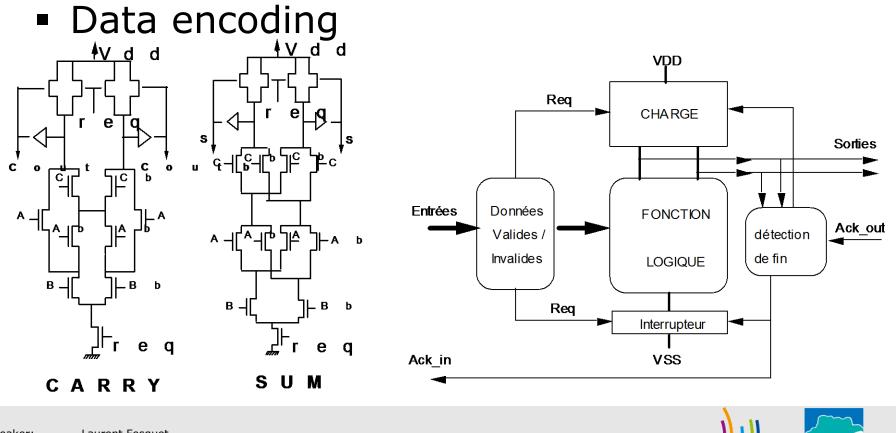

# Completion signal generation

- Internal clock (counter)

- Delay Cell

© Speaker:

Date: Page:

- Current sensing

- Data encoding

Completion signal generation

Image:Laurent FesquetSpeaker:Laurent FesquetDate:March 25, 2013Page:25

enoble 🛙

C

#### Asynchronous circuit design principles

- Completion signal generation

- Data encoding (dual rail)

Grenoble

#### Asynchronous circuit design principles

#### Completion signal generation

Speaker: Laure Date: March Page: 28

C

Laurent Fesquet March 25, 2013 28

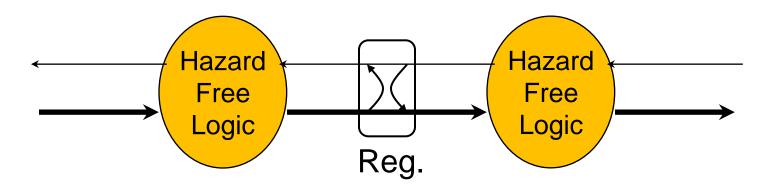

- Conclusion

- Asynchronous circuit communicate using an handshaking protocol

- Data/Request have to be encoded

- A completion signal is required

- → The implementation may be delay insensitive

- $\rightarrow$  Hazard free logic is required

- $\rightarrow$  Hardware overhead?

## Outline

- Designing synchronous circuits

- Asynchronous circuit principles

- Asynchronous circuit design principles

- Asynchronous circuit classes

- Exploiting the asynchronous logic

- Success stories

- conclusion

## **Asynchronous circuit classes**

- Hazard free logic

- QDI Circuits

- Data path: a dual-rail OR Gate

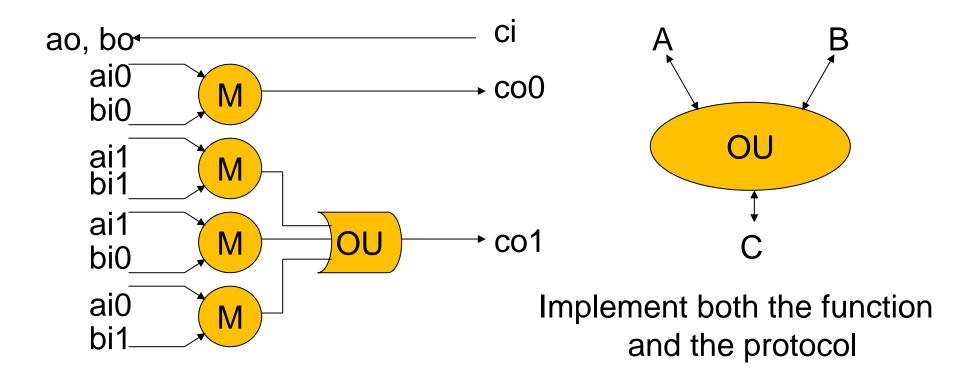

- Sequencing: the Q-Element

- Bounded delay circuits

- Huffman circuits / Burst mode circuits

- Sequencing: the Q-Element

- Micropipeline circuits

#### Asynchronous circuit classes

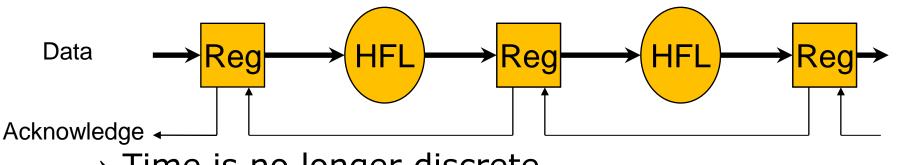

- Synchronous circuits  $Data \longrightarrow Reg \longrightarrow Log. \longrightarrow Reg \longrightarrow Reg \longrightarrow Log. \longrightarrow Reg \longrightarrow Re$

- Time is discrete

- → combinatorial logic is simple (hazards ignored)

- $\rightarrow$  trivial communication mechanism

- $\rightarrow$  worst case approach

#### **Asynchronous circuit classes**

Asynchronous circuits

#### **No global clock = No global timing assumption**

#### Sequencing is based on Handshaking

Hazard free logic is required

© Speaker: Date: Page:

Laurent Fesquet March 25, 2013 33

C Speaker: Date: Page: 34

#### **École thématique ARCHI'13**

#### Asynchronous circuit classes

- Static hazards

- Dynamic hazards

- Combinatorial hazards

Thinking and Designing Differently:

The Asynchronous Alternative

Hazard

Free

Logic

#### **Asynchronous circuit classes**

Asynchronous circuits

No global clock

No global timing assumption

**Robustness & Complexity**

more timing assumptions

Delay insensitive circuits

Hazard

Free

\_ogic

- Quasi delay insensitive circuits

- Speed independent circuits

- Huffman / Burst-mode circuits

- Micropipeline

© Speaker: Laurent Date: March 2 Page: 35

Laurent Fesquet March 25, 2013 35

are decreasing :

## **Asynchronous circuit classes**

- Hazard free logic

- QDI Circuits

- Data path: a dual-rail OR Gate

- Sequencing: the Q-Element

- Bounded delay circuits

- Huffman circuits / Burst mode circuits

- Sequencing: the Q-Element

- Micropipeline circuits

#### Asynchronous circuit classes

#### QDI Asynchronous circuits

- Functionally correct without any assumption on the wire and gate delays (unbounded delay model) except...

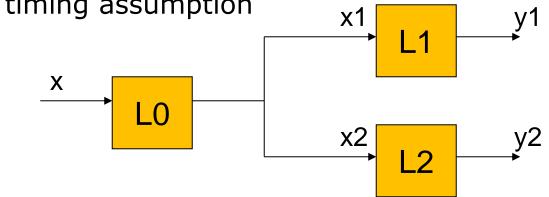

- "Isochronic fork" timing assumption

$\rightarrow$  Robustness is maximum (with respect to delay variations)

#### Asynchronous circuit classes

Speed Independent asynchronous circuits

- Functionally correct whatever the delays in the gates (unbounded delay model)

- The wires are assumed to be zero delay

- => all wires respect the isochronic fork property

- $\rightarrow$  Less accurate than the QDI model

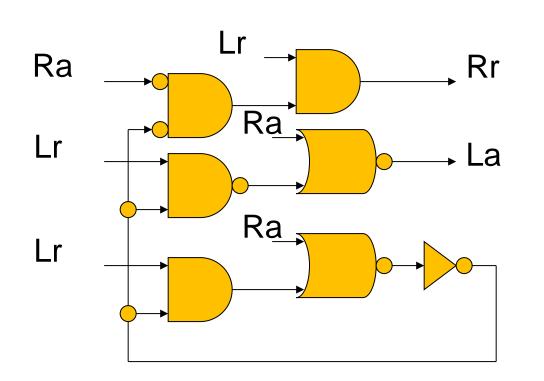

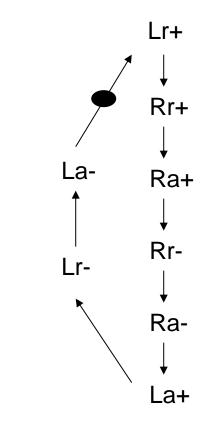

# **QDI** asynchronous circuits

#### Quasi Delay Insensitive:

hazard free control logic & hazard free data-paths

- $\rightarrow$  Time is no longer discrete

- $\rightarrow$  Hazard free logic

- $\rightarrow$  Handshake based communications

- $\rightarrow$  Mean time approach

No timing

assumption

# **QDI** asynchronous circuits

- Implementing delay insensitivity: examples

- Choice of a communication protocol (request acknowledge)

- 1 bit Channel

# **QDI** asynchronous circuits

• An example: dual-rail OR Gate

Image:Laurent FesquetSpeaker:Laurent FesquetDate:March 25, 2013Page:41

#### **QDI Asynchronous circuits**

#### **Asynchronous circuit classes**

- Hazard free logic

- QDI Circuits

- Data path: a dual-rail OR Gate

- Sequencing: the Q-Element

- Bounded delay circuits

- Huffman circuits / Burst mode circuits

- Sequencing: the Q-Element

- Micropipeline circuits

#### Huffman/Burst-mode asynchronous circuits

- The correctness depends on the gate/wire delays

- Based on the "bounded delay" model

- "Fundamental mode" assumption for the environment

C Speaker: Laurent Fesquet Date: March 25, 2013 Page: 44

Thinking and Designing Differently: The Asynchronous Alternative

#### **Burst-mode asynchronous circuits**

An example: The Q-Element

Image:Laurent FesquetSpeaker:Laurent FesquetDate:March 25, 2013Page:45

#### **Asynchronous circuit classes**

- Hazard free logic

- QDI Circuits

- Data path: a dual-rail OR Gate

- Sequencing: the Q-Element

- Bounded delay circuits

- Huffman circuits / Burst mode circuits

- Sequencing: the Q-Element

- Micropipeline circuits

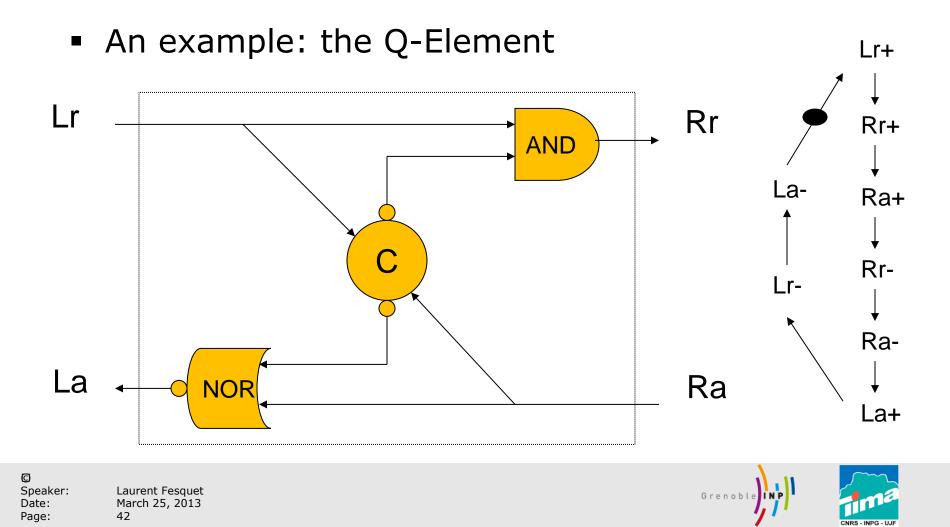

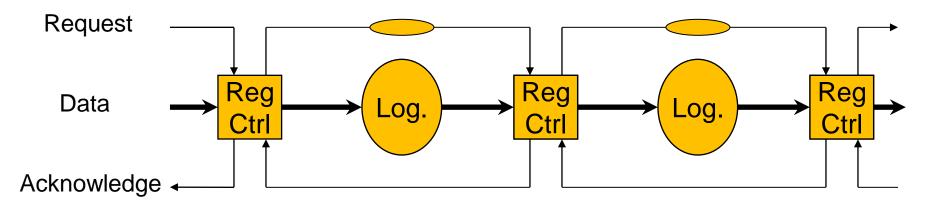

# **Micropipeline asynchronous circuits**

Micropipeline

- $\rightarrow$  Time is discrete

- $\rightarrow$  Combinatorial logic is simple

- → Communication channels (handshake based)

- $\rightarrow$  Locally worst case approach

Speaker: Laurent Fesquet Date: March 25, 2013 Page: 47

C

#### **Micropipeline asynchronous circuits**

Hazard free control logic В Standard data path F(A,B Areq Cack Delay Breq Α Reg F(A,B)B Aack rea Dela **Back**

Image: Constraint of the sector of the sec

Grenoble

# Asynchronous circuit classes

- Conclusion

- QDI circuits are the most robust with respect to delays (isochronic fork for some wires)

- Huffman & Burst-Mode circuits use the bounded delay model and require the fundamental mode

- → **QDI : Data-paths & Controllers**

- → Speed Independent / Burst-Mode: Controllers

- → Micropipeline : Standard data-path + QDI Controllers

# Asynchronous circuit classes

QDI

#### Pros

•Delay insensitive

Fast

•Low power with some design effort

•Self-testable with certain logic style

#### Cons

C

•Larger area

•Synthesis of data-paths is complex

# Micropipeline

#### Pros

- Low overhead

- •Synthesis of data-path is performed using commercial tools

- •Low power with some design effort

#### Cons

- •Not delay insensitive

- •Not very fast

- •Some parts are difficult to test (delay fault)

Speaker: Laurent Date: March 2! Page: 50

Laurent Fesquet March 25, 2013 50

#### Outline

- Designing synchronous circuits

- Asynchronous circuit principles

- Asynchronous circuit design principles

- Asynchronous circuit classes

- Exploiting the asynchronous logic

- Success stories

- conclusion

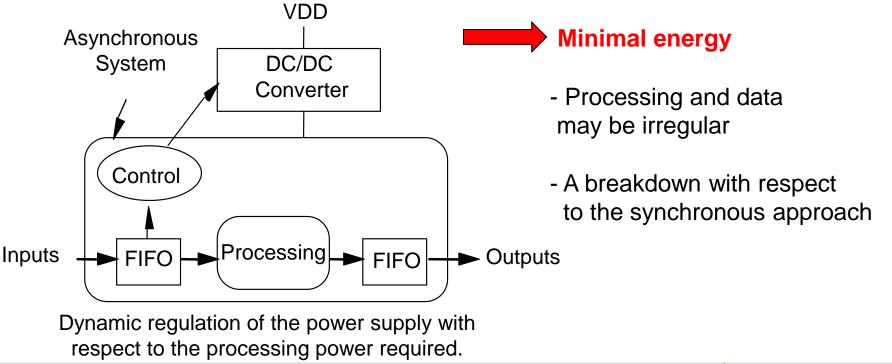

# **Asynchronous circuits**

- Fast

- speed only depends on the circuit complexity

- Low power, low noise

- data driven (only the processing part consumes power)

- Distributed processing in space and time

- Area

- complexity depends on the asynchronous logic style

- Safe and secure

- Robust to PVT variations

- Less sensitive to DPA and FA

# **Modularity and Locality**

SoCs design is easier: (reduced Time-to-Market)

- Distributed control (protocol implementation)

- Delay insensitive communications between modules

- Modules are independent from each other in terms of:

- Functionality (global state not known)

- Speed (maximum speed)

- Activity (power)

- Noise (uncorrelated current consumption)

- Scalability

© Speaker: Date: Page:

Laurent Fesquet March 25, 2013 53

Frenoble IN

Modularity

Reusability

Scalabilit

# **On-chip communication systems**

- Multiple Clock Domains (GALS) Metastability may occur at clock domain boundaries

- Control the Mean Time Between Failure (MTBF)

- Non adaptive synchronization

- Adaptive synchronization  $\rightarrow$  Probability of error is not zero

- Avoiding metastability

- Stretchable clocks

- → Probability of error is zero

- Fully asynchronous (GALA)

Issues: reliability and latency

C

# Automatic performance regulation

Computation-power controlled systems : E = a.fCV<sup>2</sup>

© Speaker: La Date: Ma Page: 55

Laurent Fesquet March 25, 2013 55

© Speaker: Date: Page:

Thinking and Designing Differently: The Asynchronous Alternative

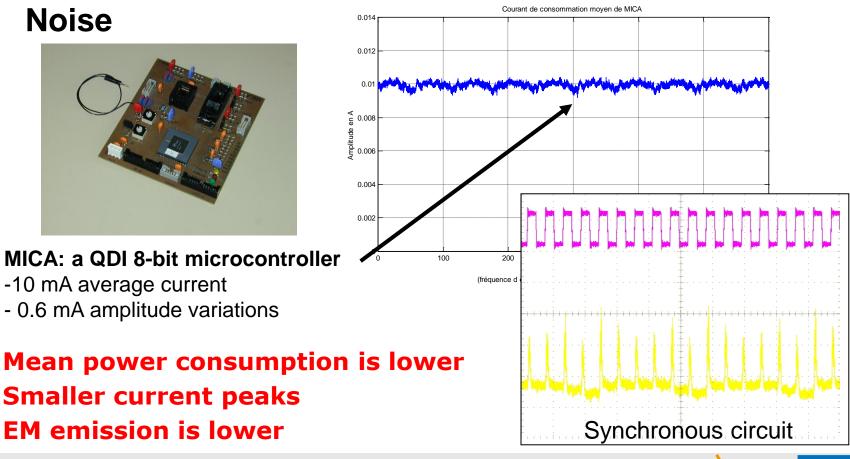

#### Exploiting the asynchronous logic

#### Security

Processor MICA

© Speaker: Date: Page:

Laurent Fesquet March 25, 2013 57

#### Outline

- Designing synchronous circuits

- Asynchronous circuit principles

- Asynchronous circuit design principles

- Asynchronous circuit classes

- Exploiting the asynchronous logic

- Success stories

- conclusion

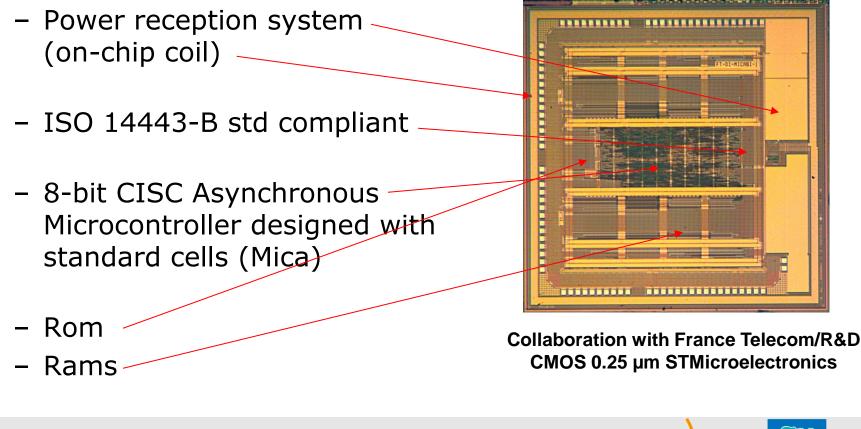

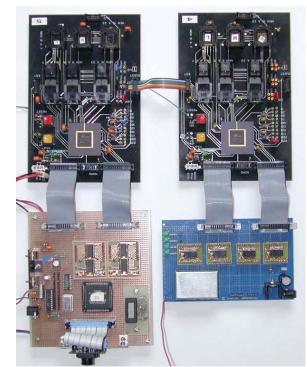

#### **SoC for Contactless Smart-Card**

Laurent Fesquet March 25, 2013 59

#### **SoC for Contactless Smart-Card**

- Asynchronous Logic relaxed Design constraints

- Not sensitive to supply voltage variations

- → Power reception system (capacitances area, voltage regulation)

- Lower current peaks

- → The Micro-controller can be running during the communications without disturbing the load modulation.

- Maximum processing power delivered according to the power received

Collaboration with France Telecom/R&D CMOS 0.25 µm STMicroelectronics

Speaker: Laurent Fesquet Date: March 25, 2013 Page: 60

C

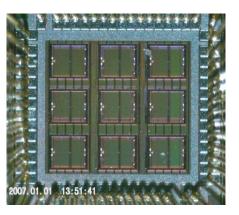

#### **MICA** information sheet

- CMOS 0.25 µm

- 1-of-4 DI codes for arith. and reg.

- 1-of-n DI codes for the control

- Complexity

- 145 000 transistors

- 1 M transistors with memories

- 13 mm<sup>2</sup> with pads (prototype)

- PGA120 package for the prototype

#### – Test

- BIST (approx. 300 instr)

- functional at 1<sup>er</sup> silicon between 3v et 0.65 v

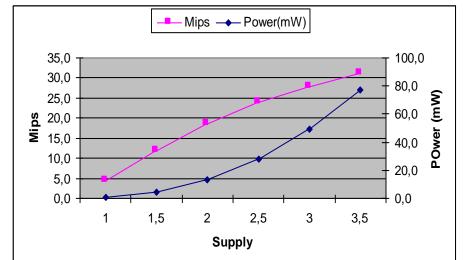

- 24 Mips / 28 mW @ 2.5V

- 4,3 Mips / 800 μW @ 1V

| Supply(V) | Mips | Core Current (mA) | Power(mW) | Mips/Watt |

|-----------|------|-------------------|-----------|-----------|

| 1         | 4,3  | 0,8               | 0,8       | 5503,6    |

| 1,5       | 11,9 | 3,1               | 4,7       | 2560,2    |

| 2         | 18,6 | 6,7               | 13,3      | 1398,0    |

| 2,5       | 23,8 | 11,2              | 28,0      | 850,3     |

| 3         | 27,8 | 16,3              | 48,9      | 568,1     |

| 3,5       | 31,3 | 22,0              | 77,0      | 405,8     |

Thinking and Designing Differently: The Asynchronous Alternative

#### And many other circuits ...

#### **ASPRO (ASynchronous PROcessor)**

- 16-bit RISC processor

- 140 MIPS

- QDI asynchronous logic

- Standard Cells

- 500 KTr for the core

- 6.3 MTr with memories

- Total area is 42 mm<sup>2</sup>

- CMOS 0.25µm 6 metal layers

STMicroelectronics

C

Grenoble

Thinking and Designing Differently: The Asynchronous Alternative

#### And many other circuits ...

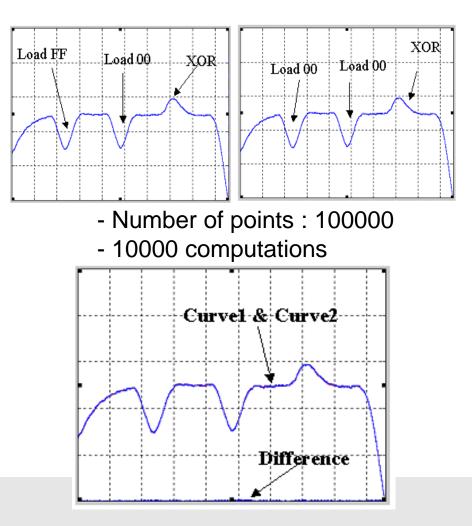

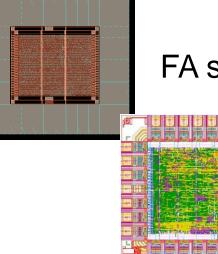

FA secured DES circuit (CMOS ST 65 nm)

#### DPA secured DES circuit (CMOS ST 65 nm)

# The first world secured FPGA (DPA) (CMOS ST 65 nm)

© Speaker: Lau Date: Ma Page: 63

Laurent Fesquet March 25, 2013 63

#### And many other circuits ...

#### Low-phase noise multiphase asynchronous oscillator (CMOS ST 65 nm)

| N° of<br>stages | Т/В    | Freq.<br>(GHz) | Consum.<br>(mW) | PN at 1M<br>(dBc) | PN at 10M<br>(dBc) |

|-----------------|--------|----------------|-----------------|-------------------|--------------------|

| 3               | 2T/1B  | 3.95           | 0.454           | -82.97            | -109.07            |

| 6               | 4T/2B  | 3.95           | 0.908           | -85.98            | -112.08            |

| 12              | 8T/4B  | 3.95           | 1.817           | -88.99            | -115.09            |

| 24              | 16T/8B | 3.95           | 3.635           | -92               | -118.1             |

| N° of<br>stages | Т/В   | Frequ.<br>(GHz) | Comsu.<br>(mW) | N° of<br>phases | Resolution<br>(ps) | PN at 1<br>MHz |

|-----------------|-------|-----------------|----------------|-----------------|--------------------|----------------|

| 9               | 4/5   | 6.41            | 1.94           | 9               | 17.3               | -82.9          |

| 21              | 10/11 | 6.16            | 4.47           | 21              | 7.7                | -87.6          |

| 41              | 20/21 | 6.02            | 8.62           | 41              | 4                  | -90.7          |

Speaker: Date: Page: 64

C

Grenoble

#### Outline

- Designing synchronous circuits

- Asynchronous circuit principles

- Asynchronous circuit design principles

- Asynchronous circuit classes

- Exploiting the asynchronous logic

- Success stories

- conclusion

# Conclusion

Designing asynchronously means:

- Channel-based SoCs instead of clock-based

- Delay-insensitive or reduced timing assumptions

- Event-driven instead of clock-driven

- $\rightarrow$  Low-power, low-noise

- $\rightarrow$  Modularity, locality, scalability, reusability

- $\rightarrow$  Reliability, safety, security

- $\rightarrow$  Reduced design time (TTM)

#### • Are fully asynchronous systems the future?

→ Synergy between sensors, actuators, interfaces and processing

Image: Constraint of the second sec

#### **Towards Fully Asynchronous Systems?**

- Many startups: Handshake Solutions, Fulcrum, Theseus logic, stilistix, Tiempo, ...

- one spin-off from TIMA!

. . .

Intel recently acquired Fulcrum microsystems

Thinking and Designing Differently: The Asynchronous Alternative

#### Thinking and Designing Differently: The Asynchronous Alternative

# **Thanks for your attention!**

© Speaker: Lau Date: Ma Page: 68

Laurent Fesquet March 25, 2013 68